hello, i love the interview on the Moore's law is dead. i have a question regarding fab like TSMC. what is their plan after 1nm if we ever go beyond that. Daniel said Apple required a new node (if i remember it correct) and Intel can't keep up and that's why TSMC is doing it half step (?) to satisfied Apple. what happens after 1nm?

Array

(

[content] =>

[params] => Array

(

[0] => /forum/index.php?threads/naming-beyond-1nm.13416/

)

[addOns] => Array

(

[DL6/MLTP] => 13

[Hampel/TimeZoneDebug] => 1000070

[SV/ChangePostDate] => 2010200

[SemiWiki/Newsletter] => 1000010

[SemiWiki/WPMenu] => 1000010

[SemiWiki/XPressExtend] => 1000010

[ThemeHouse/XLink] => 1000970

[ThemeHouse/XPress] => 1010570

[XF] => 2021370

[XFI] => 1050270

)

[wordpress] => /var/www/html

)

Guests have limited access.

Join our community today!

Join our community today!

You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please, join our community today!

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Naming beyond 1nm?

- Thread starter soAsian

- Start date

hello, i love the interview on the Moore's law is dead. i have a question regarding fab like TSMC. what is their plan after 1nm if we ever go beyond that. Daniel said Apple required a new node (if i remember it correct) and Intel can't keep up and that's why TSMC is doing it half step (?) to satisfied Apple. what happens after 1nm?

Be sure and check out our new podcast series. Our second episode is about Moore's Law.

In regards to process naming, ever since FinFETs arrived the names are made up and have no technical significance. Remember, previously process names were based on transistor length. With FinFets that is not possible.

So, to answer your question, what happens after 1nm? We will make up new numbers based on what the marketing people come up with since they are no longer reality based.

Good question though and I will spend some more time on it, absolutely.

John Grant (Nine Tiles)

Member

That's a shame. I really liked the idea of watching my fingernail creeping across the chip (it grows at about 1nm/sec).previously process names were based on transistor length. With FinFets that is not possible

So features aren't getting smaller? (Comforting, as they were heading towards single molecules.) What does change from one process node to the next? And will we need to move from software run on CPUs to FPGA logic to get the processing power / electrical power ratio up?

Hey Daniel, where can we find information about this new podcast series? I searched for it but the following link from your twitter feed seems broken: https://semiwiki.com/?p=293910Be sure and check out our new podcast series. Our second episode is about Moore's Law.

In regards to process naming, ever since FinFETs arrived the names are made up and have no technical significance. Remember, previously process names were based on transistor length. With FinFets that is not possible.

So, to answer your question, what happens after 1nm? We will make up new numbers based on what the marketing people come up with since they are no longer reality based.

Good question though and I will spend some more time on it, absolutely.

Hey Daniel, where can we find information about this new podcast series? I searched for it but the following link from your twitter feed seems broken: https://semiwiki.com/?p=293910

The first podcast will be posted Jan 2nd (it will look like a blog with a sound file inside), and they will run every Saturday. We are having fun so far. I think the content is good so it should be a regular series:

Welcome to the Semiconductor Insiders Podcast Series!

The goal of this Podcast Series is to bring semiconductor experts together to get to the truth about the matter at hand. We’ll get right to the point and not exceed 30 minutes of your time. If you have a topic you would like us to cover please post it on SemiWiki.com and we will get right to it.

First topic: Why are Semiconductors so Sexy?

Second topic: Did FinFETs Kill Moore's Law? With Wally Rhines

Third topic: What Happens Next in The Processor Wars? With Jim Hogan

Fourth Topic: Can China Really Become Self-Sufficient in Semiconductors? Robert Maire

Future topics include:

Is the Intel Setback Temporary or Terminal?

Chiplets are cheating!

Data Becomes the New Oil

Innovations in Cybersecurity (The Next Wave of Secure Data)

Are ASICs Dead?

COVID Backlash for Emerging Technology Companies

The New Wave of Semiconductor Consolidation: Where Does It Lead?

Domain Specific vs General Purpose Chips?

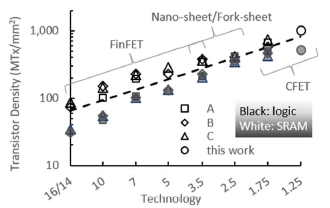

Scott Jones is sticking with the Moore's Law 0.7X multiplier for each node, assuming that the foundries find a way to stay (roughly) on the transistor density curve. Here's a graph he recently published:

So, the next point on Scott's curve would be: 1.25 * 0.7 = 0.875... unfortunately the "0.875 node" doesn't really roll off the tongue.

Note that in Scott's curve, he has FinFETs transitioning to GAA nanosheets for a couple of process node generations, then transitioning to Complementary FETs (CFETs) in the 2028 timeframe (or thereabouts).

At a 10,000 foot level, CFETs are kind of similar to nanosheets, further extending the vertical stacking. So, if CFETs do indeed emerge as the next device type, perhaps the nomenclature should indicate how the vertical stack is constructed... perhaps something like: 1p2n (for one pMOS GAA nanosheet, with two nMOS nanosheets stacked on top). Append something indicating the first level metal pitch, and you've got a winner for a 19nm metal pitch: "1p2n19MP". Of course, the foundry marketing teams will never buy into describing that kind of detail.

Looking again at Scott's chart, perhaps a better descriptor is to go with the transistor density below the "1.25nm node"... say, the "1B" node, for 1 billion transistors per mm**2. Now that's something marketing could latch onto... one billion transistors per sq. mm. has a nice ring to it. And, successive nodes could reflect that transistor density increase -- something like the "1.3B" node.

Then again, if CFETs are overtaken by a more esoteric technology, such as 2D MoS2 devices or 1D carbon nanosheets, then something different is perhaps appropriate... perhaps using the cellular "generation" nomenclature... e.g., "1G CNT", "2G CNT", etc.

Consider how obscure the cellular "5G" network performance is actually turning out to be, this may be a good way to hide the actual details of the underlying technology.

So, the next point on Scott's curve would be: 1.25 * 0.7 = 0.875... unfortunately the "0.875 node" doesn't really roll off the tongue.

Note that in Scott's curve, he has FinFETs transitioning to GAA nanosheets for a couple of process node generations, then transitioning to Complementary FETs (CFETs) in the 2028 timeframe (or thereabouts).

At a 10,000 foot level, CFETs are kind of similar to nanosheets, further extending the vertical stacking. So, if CFETs do indeed emerge as the next device type, perhaps the nomenclature should indicate how the vertical stack is constructed... perhaps something like: 1p2n (for one pMOS GAA nanosheet, with two nMOS nanosheets stacked on top). Append something indicating the first level metal pitch, and you've got a winner for a 19nm metal pitch: "1p2n19MP". Of course, the foundry marketing teams will never buy into describing that kind of detail.

Looking again at Scott's chart, perhaps a better descriptor is to go with the transistor density below the "1.25nm node"... say, the "1B" node, for 1 billion transistors per mm**2. Now that's something marketing could latch onto... one billion transistors per sq. mm. has a nice ring to it. And, successive nodes could reflect that transistor density increase -- something like the "1.3B" node.

Then again, if CFETs are overtaken by a more esoteric technology, such as 2D MoS2 devices or 1D carbon nanosheets, then something different is perhaps appropriate... perhaps using the cellular "generation" nomenclature... e.g., "1G CNT", "2G CNT", etc.

Consider how obscure the cellular "5G" network performance is actually turning out to be, this may be a good way to hide the actual details of the underlying technology.

hello, i love the interview on the Moore's law is dead. i have a question regarding fab like TSMC. what is their plan after 1nm if we ever go beyond that. Daniel said Apple required a new node (if i remember it correct) and Intel can't keep up and that's why TSMC is doing it half step (?) to satisfied Apple. what happens after 1nm?

What Si says? Picometers!