Multi-die design is not a new concept. It has been around for a long time and has evolved from 2D level integration on to 2.5D and then to full 3D level implementations. Multiple driving forces have led to this progression. Whether the forces are driven by market needs, product needs, manufacturing technology availability or EDA tools development, the progression has been picking up speed. With the slowing down of Moore’s law, the industry has entered a new era. While there is not yet an industry-wide term, Synopsys uses SysMoore as a shorthand notation to refer to this era.

Synopsys gave a presentation at DAC 2021 on addressing the market demands of the SysMoore era. The presentation gave excellent insights into their strategy for delivering solutions. Six vectors were identified as efficiency roadmap drivers to power the SysMoore Era and what solutions the various market segments are demanding. New complexities and opportunities were highlighted for advances all around and what Synopsys is bringing out in terms of new technologies for this era. A recent post provides a synopsis of that entire talk.

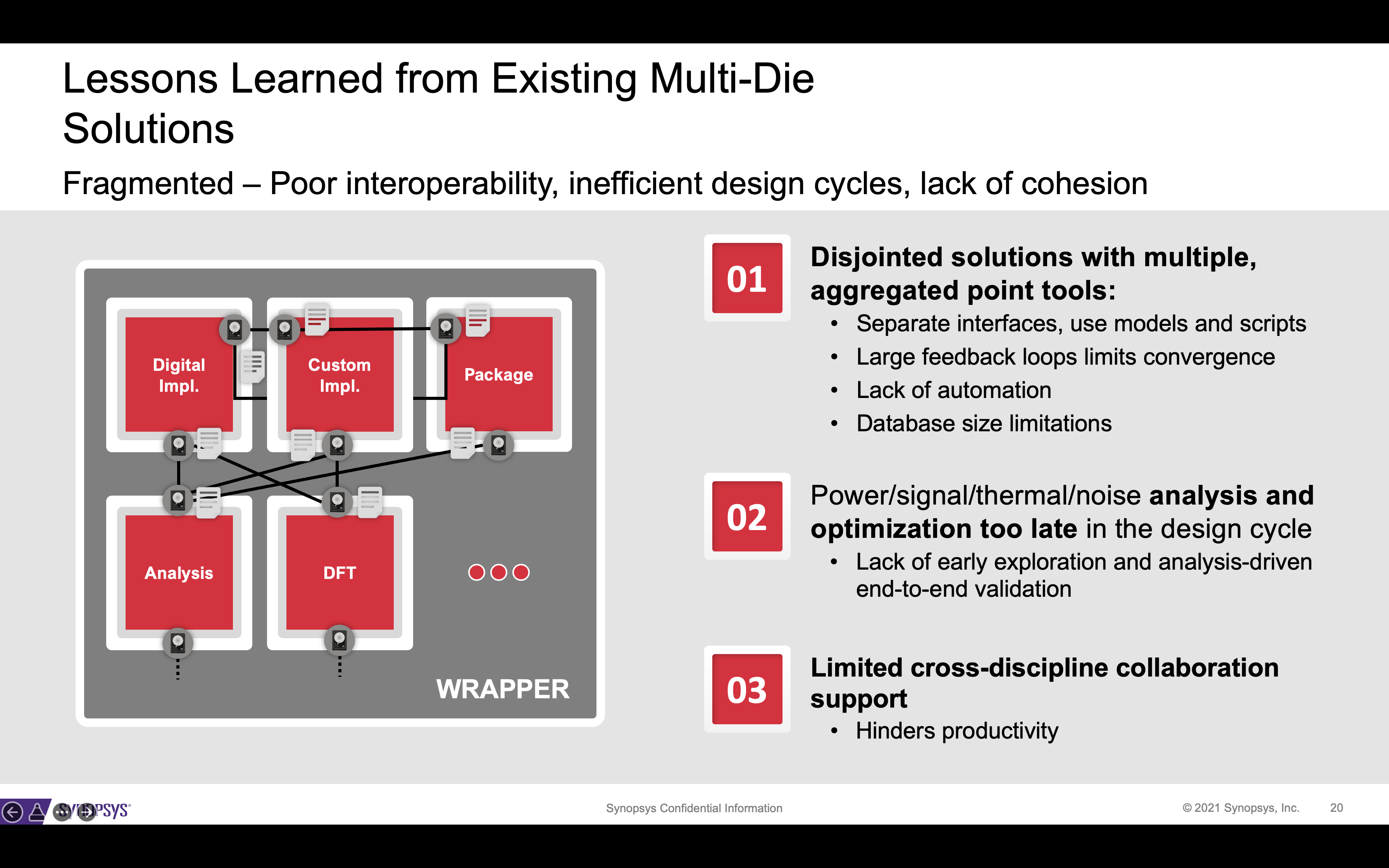

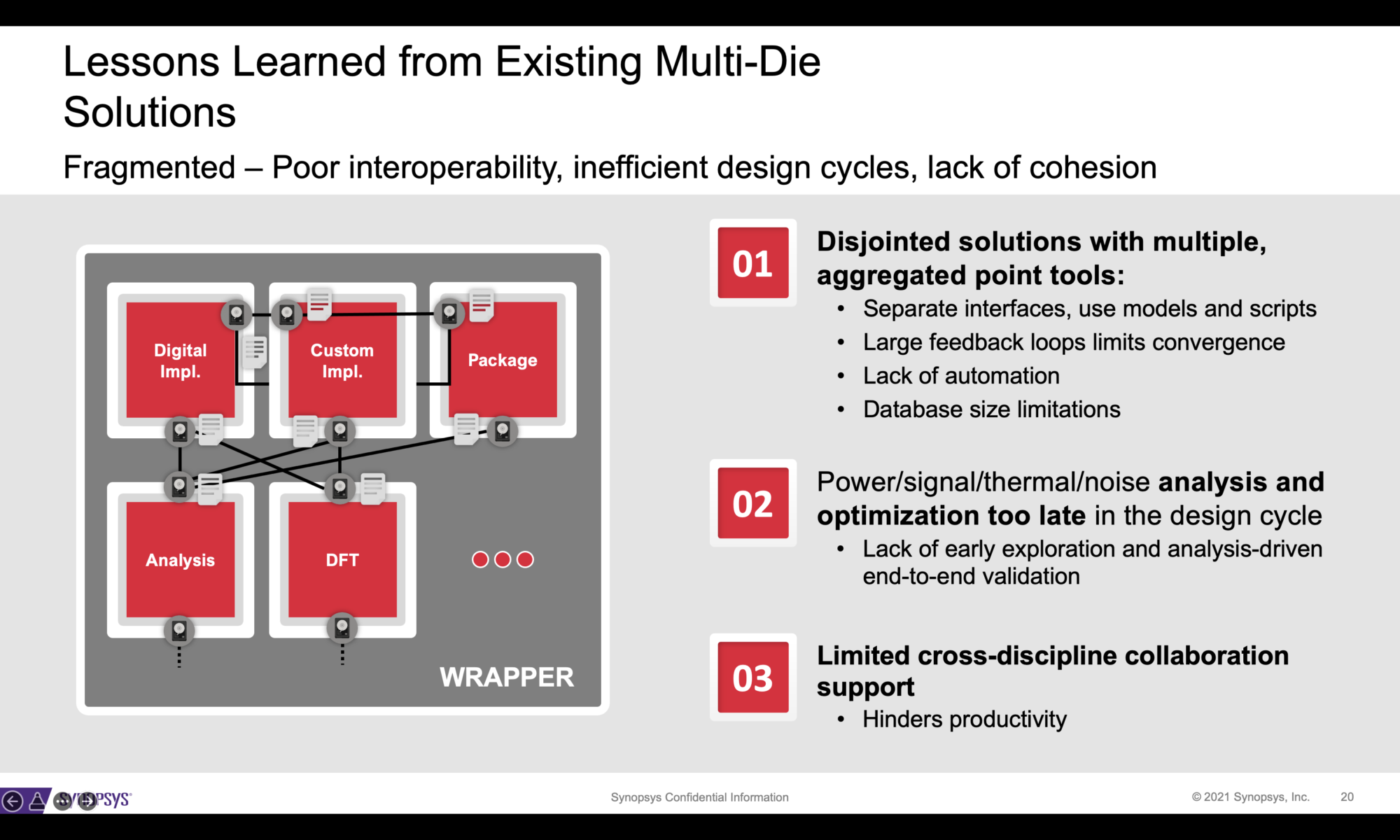

One of the efficiency drivers identified relates to memory and I/O latency, multi-lane HBMs and Phys on multi-die designs. In the SysMoore era, high performance computing (HPC) is fast becoming a major driver of multi-die/3DIC designs for multiple reasons. There is no let-up on the increasing need for functionality integration and performance enhancement. At the same time, integrating everything on a single large die may not be the most viable option sub 7nm nodes. This opens up the opportunity to implement a multi-die design and still optimize for PPA, latency, cost and time-to-market schedule. At the same time, there are many challenges to overcome when doing multi-die designs. Refer to Figure below for drawbacks of existing multi-die solutions.

These challenges cause slow convergence and sub-optimal PPA/mm3.

Solution

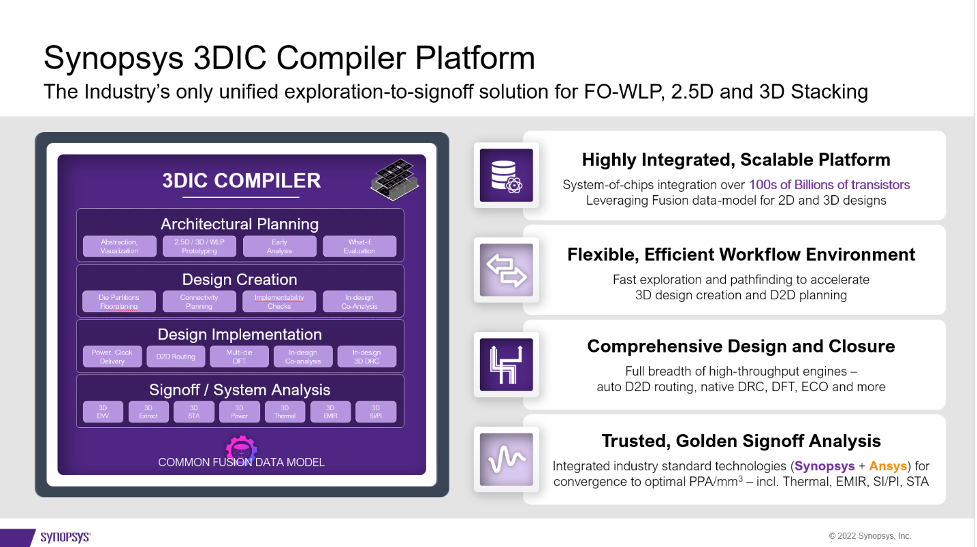

An effective cross-discipline collaboration is needed for converging to an optimal solution. What is needed is a platform that enables a consistent and efficient exchange of information. A solution that offers a GUI-driven 3D visualization, planning and design. One that implements DRC-aware routing and shielding and supports HBM. A platform that leverages a single data model that allows for fast exploration and pathfinding to accelerate the design process. A solution that enables an integrated golden-signoff that includes multi-die analysis of signal integrity, power integrity, thermal integrity, timing integrity and EMIR.

Synopsys 3DIC Compiler

While the following slide provides a high-level summary of features and benefits, you can learn more at an upcoming webinar.

About the Webinar

Synopsys will be hosting a Webinar on Feb 10, 2022 about their 3DIC Compiler (3DICC) solution. The event will cover designing HBM3 into high performance computing designs using a multi-die approach. It will cover the what-if analysis, floor planning, implementation, HBM3 channel D2D routing and analysis and simulation/signoff aspects.

What You Will Hear, See and Learn?

- HBM3 overview and HBM3 design example

- Relevance of the 3DICC features/benefits to HPC designs

- 2.5D/3D architecture evaluation

- Ansys Redhawk-SC ElectroThermal multi-physics simulation integration with 3DICC platform

- Two live demos, showcasing the ease of use and advanced auto die-to-die (D2D) routing capabilities

- Live Q&A session for attendees

Who Should Attend?

- System Architects

- Engineering Managers

- Chip Development Engineers

Registration Link: You can register for the Webinar here.

Also read:

Identity and Data Encryption for PCIe and CXL Security

Heterogeneous Integration – A Cost Analysis

Delivering Systemic Innovation to Power the Era of SysMoore

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.