DesignCon has grown over the years to become a true system design show. The show’s tagline is WHERE THE CHIP MEETS TO BOARD. This is just the beginning. Besides the chip and the board there are all the challenges, opportunities, and options to get signals reliably propagated throughout the entire system. Power, signal integrity, advanced materials and communication channels are just some of the topics to be explored. Samtec focuses on delivering the technology to implement high performance, low loss communication channels, so they fit the show well. There’s more to the story, however. In a past life, I did many trade shows with Samtec. I can tell you they are superb at building a strong presence at any show. Their partner ecosystem, compelling demos and in-depth tech talks all contribute to a high-profile presence. DesignCon is no different. My message is simple – Samtec dominates DesignCon 2021.

DesignCon is being held this week from August 16 – 18, 2021 at the San Jose McEnery Convention Center. That’s not a misprint; DesignCon will hold a live event this year. You can learn more about the show, including how to register here. As memorialized in the banner of this post, you can find Samtec at booth 907. Before I get into what they’ll be doing at the show, I want to mention that Samtec typically has fun giveaways. A word to the wise – get there early in case they run out. Let’s look at the substantial footprint Samtec will have at DesignCon.

Demos in Booth 907

Samtec comes to any trade show with a lot of compelling demonstrations, staffed by knowledgeable folks who can actually answer the hard questions. A nice part of the strategy is to promote their partner ecosystem. I personally was the recipient of this great hospitality in a prior company. Here’s a summary of their featured demos and who they will collaborate with:

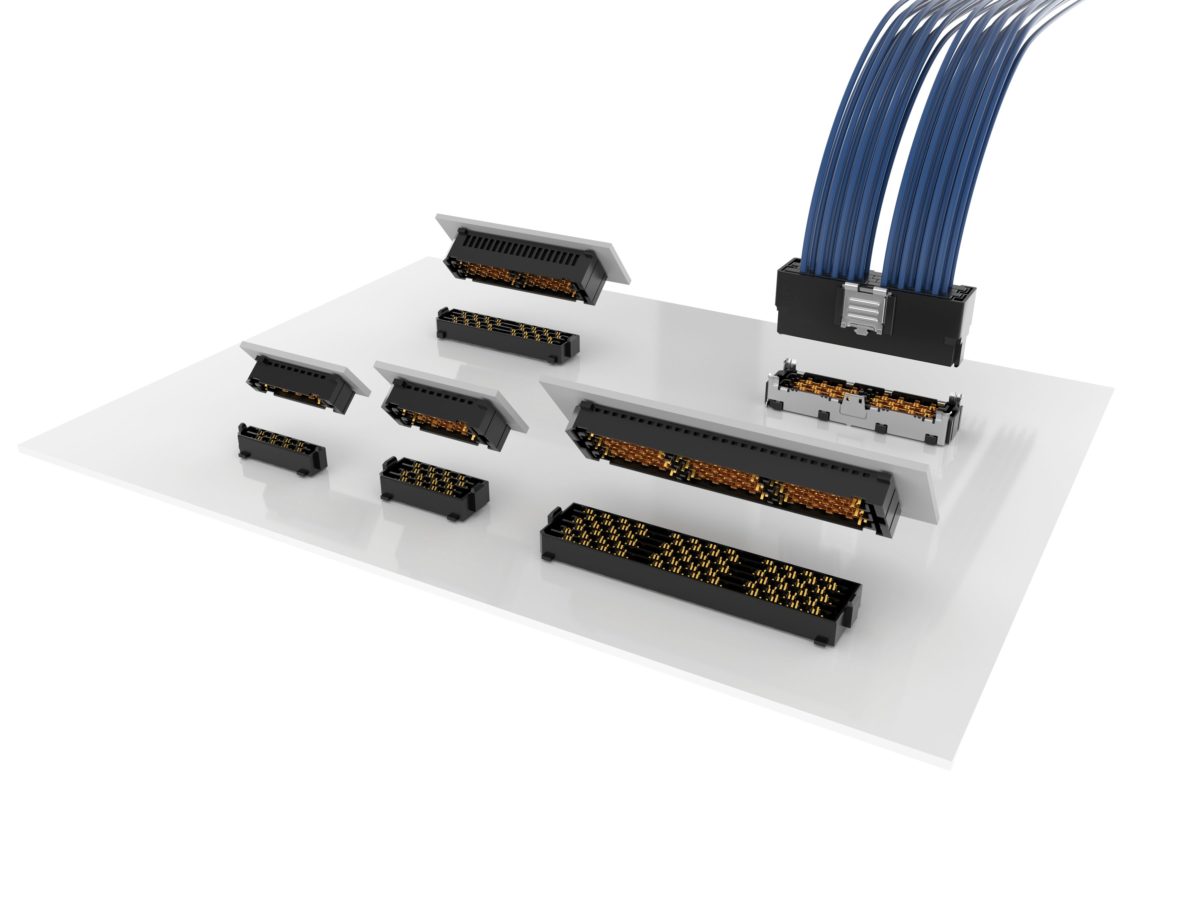

- 112G PAM4 with Alphawave: The innovative design of Samtec’s NovaRay® Arrays combines extreme density and extreme performance, which is critical as system sizes decrease and speeds increase. The fully shielded differential pair design contributes to the industry-leading 4.0 Tbps aggregate data rate.

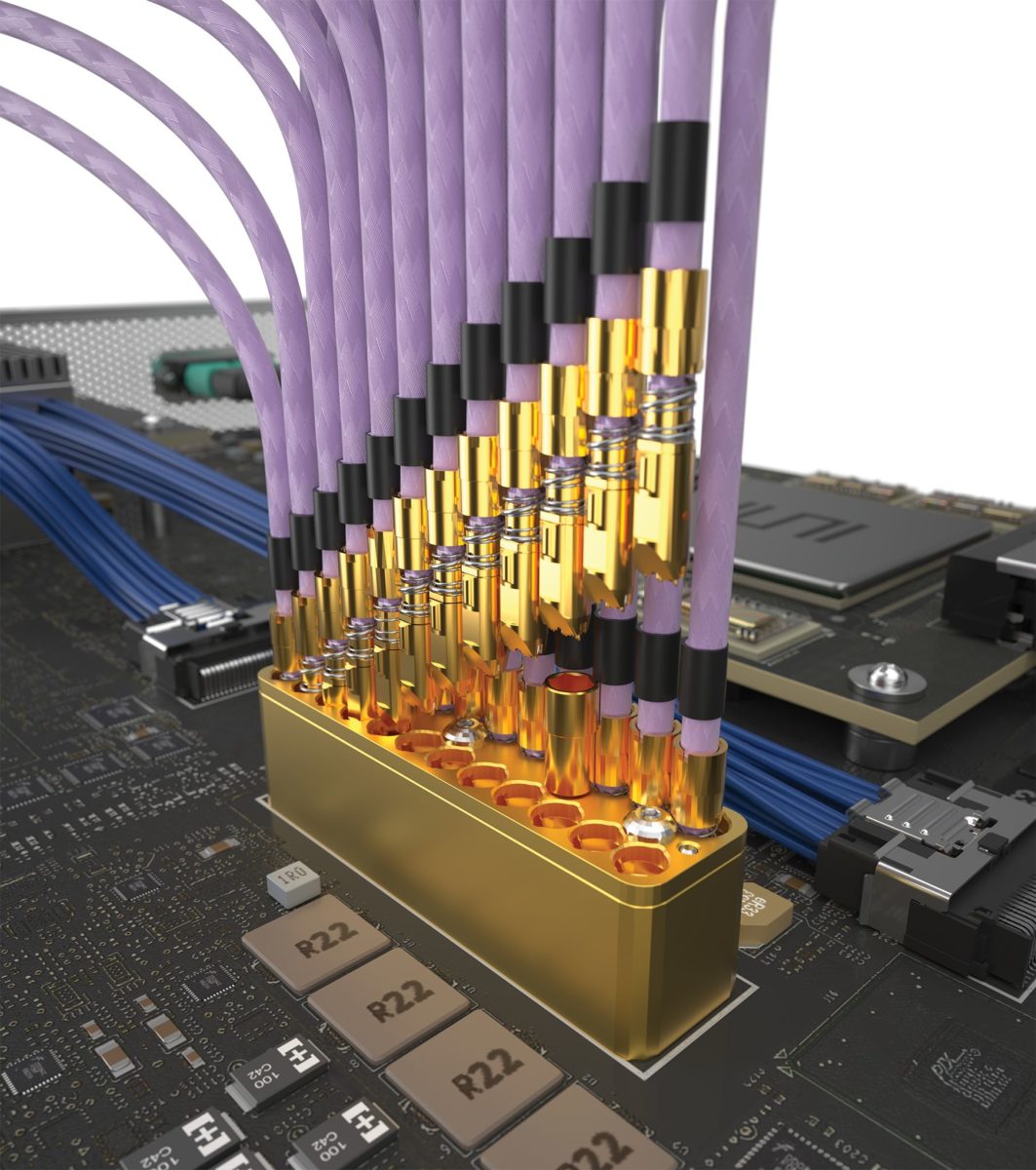

- 112G PAM4 with Xilinx: This inside-the-box, flyover demonstration highlights both precision RF 70 GHz Bulls Eye® High-Performance Test System and NovaRay cable assemblies.

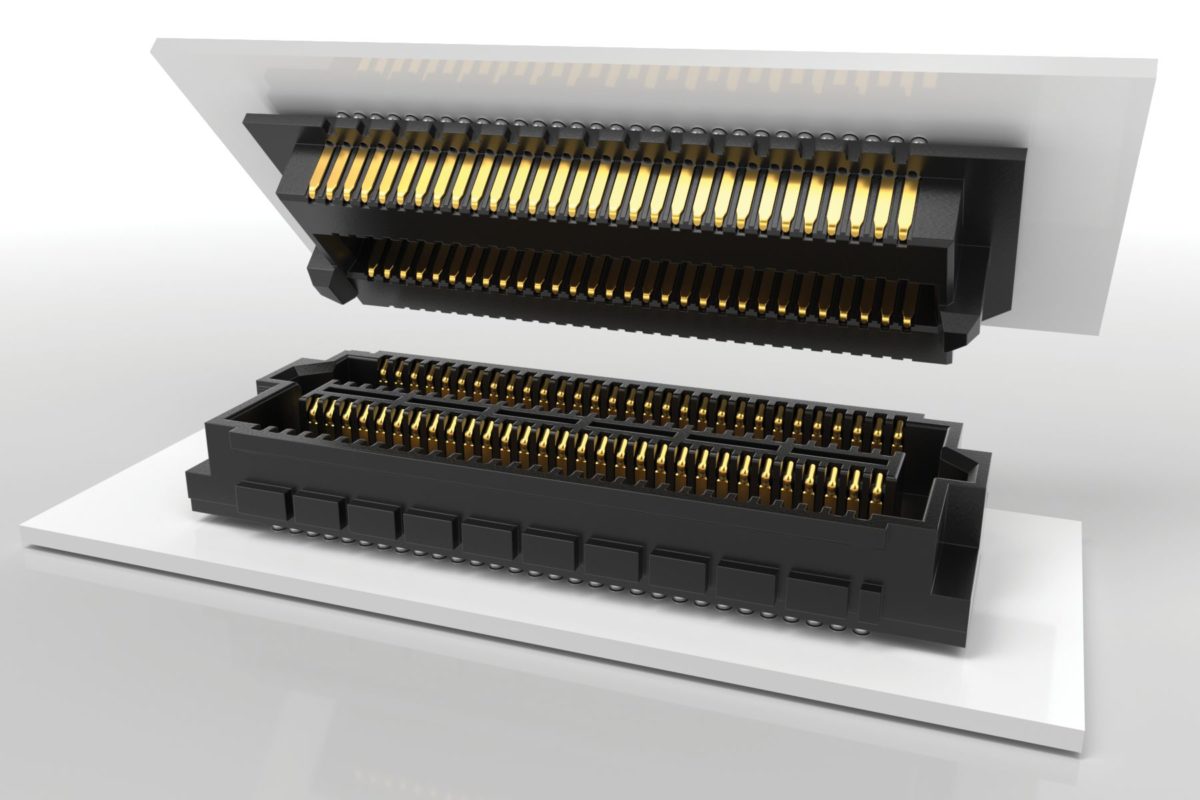

- 64G PAM4 (PCIe®0) and 112G PAM4 with Synopsys: There are two demos. The first features Samtec’s Gen-Z compliant 0.60 mm Edge Rate® High-Speed Edge Card Connector. Samtec’s 70 GHz Bulls Eye will carry the signal from a Synopsys PCIe 6.0 test chip to the mated edge card assembly. The second combines Samtec AcceleRate® HP High-Performance Arrays with a Synopsys 112G PAM4 transceiver test chip.

- V-band/60GHz, Flexible waveguide with Vubiq: This proof-of-concept V-band demonstration will run actual 10 Gbps Ethernet modulated traffic at 60 GHz through Samtec’s flexible waveguides, using Vubiq’s Haul Pass V10G product mainboard and Analog Devices HMC 6300 and 6301 chipsets.

Beyond the show floor, Samtec also dominates the technical sessions.

Technical Presentations

- Tuesday, August 17 • 8:00 AM – 8:40 AM Specification-based IBIS-AMI model PCIe 5.0 32 GT/s.Samtec will demonstrate how to convert electrical specification documents for PCIe 5.0 32 GT/s and generate an equivalent IBIS-AMI model to represent the significant electrical signaling behaviors.

- Tuesday, August 17 • 11:10 AM – 11:50 AM A Case Study in the Development of a 112 Gbps-PAM4 Silicon & Connector Test Platform. The continued progression to higher data rates puts increasing demands on the design of practical Serdes channels. At 112G-PAM4, the UI is only 17.86 ps, and signal transmission in the PCB must be highly optimized for loss, reflections, crosstalk, and power integrity.

- Tuesday, August 17 • 2:00 PM – 2:40 PM Hidden Secrets of IBIS Sampling Specifications. The I/O Buffer Information Specification-Algorithmic Modeling Interface (IBIS-AMI) enables sharing of a model, which encompasses the complexity of the transmitter and receiver blocks. The IBIS-AMI model outputs an equalized waveform along with sampling information for the EDA tool.

- Tuesday, August 17 • 3:00 PM – 3:40 PM Design Case Study & Experimental Validation for a 100 Gb/s Per Lane C2M Link Using Channel Operating Margin. The Chip-to-Module (C2M) interface as specified by the IEEE 802.3 Standard Working Group, and currently being updated for higher data rates, implements links that must perform up to 800 Gb/s (8 × 100 Gb/s) within the internet infrastructure physical layer. The design of these channels requires multiple engineering disciplines that fused together to create a comprehensive workflow.

- Wednesday, August 18 • 9:00 AM – 9:40 AM Impact of Power Plane Termination on System Noise. To reduce power rail voltage fluctuations that could lead to noise emissions, it is critical to keep the power plane’s impedance below a target and minimize impedance peaks over frequency. Previous studies have shown that RC power plane termination can reduce power plane impedance peaks, including on an electrically dense production board where decoupling capacitors would not fit near-critical memory components.

And to round out the agenda:

Panel Discussions

- Monday, August 16 • 4:45 PM – 6:00 PM Panel — PCIe 6.0: New Challenges & New Tests for an Old Standard. The consumer and market demand for higher data throughput has been pushing industries and standards to increase data rates. The evolution of other standards has also been pushing technologies such as PCIe to higher data rates. PCIe 5.0 with data rate of 32 GTps had already introduced many signal integrity and design challenges.

- Tuesday, August 17 • 4:00 PM – 5:15 PM Panel — Avoiding Disaster: Planning for Laminate Electrical Properties as a Function of Temperature. How much variation should be expected and what should OEM designers of high-speed systems do to accommodate these variations in pre-prototype signal-integrity simulations?

Now you know at least some of what Samtec will be doing at DesignCon. If you are engaged in any form of system design, this is a must-attend event. My prior warning still applies; get ready, Samtec dominates DesignCon 2021.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.