- This event has passed.

Digital Debug for FPGA/ASIC & DFT Designers Webinar

January 23, 2020 @ 10:00 AM - 11:00 AM

FREE

Overview:

Learn how to significantly reduce time needed to troubleshoot and root cause ASIC/FPGA Design & DFT issues in RTL & Gate level designs.

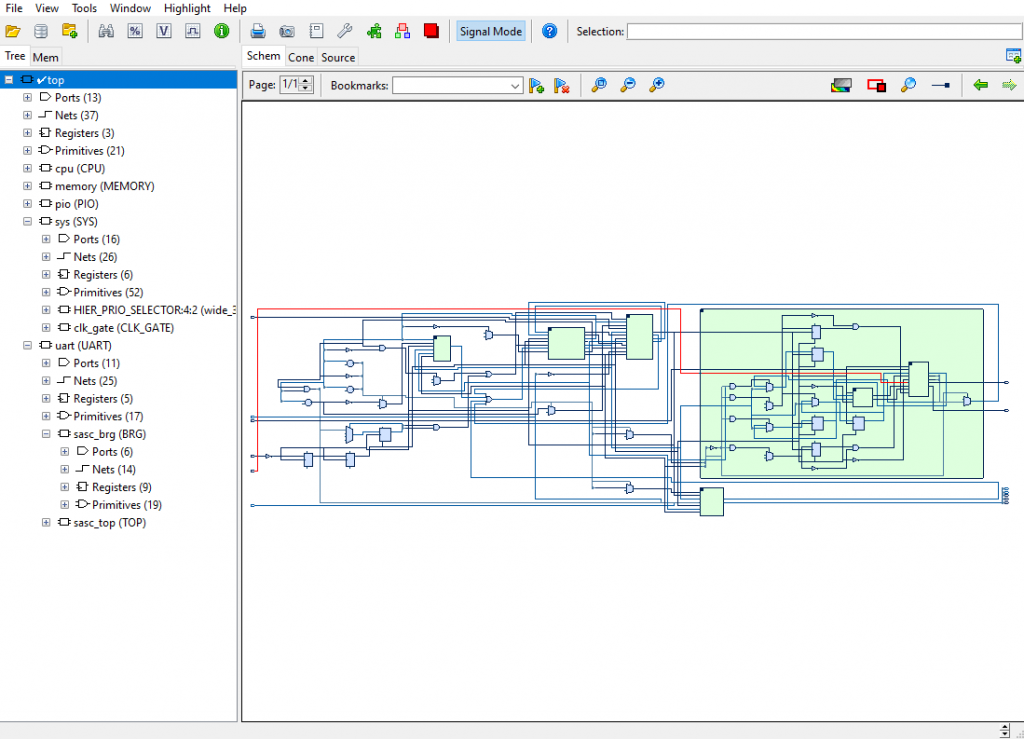

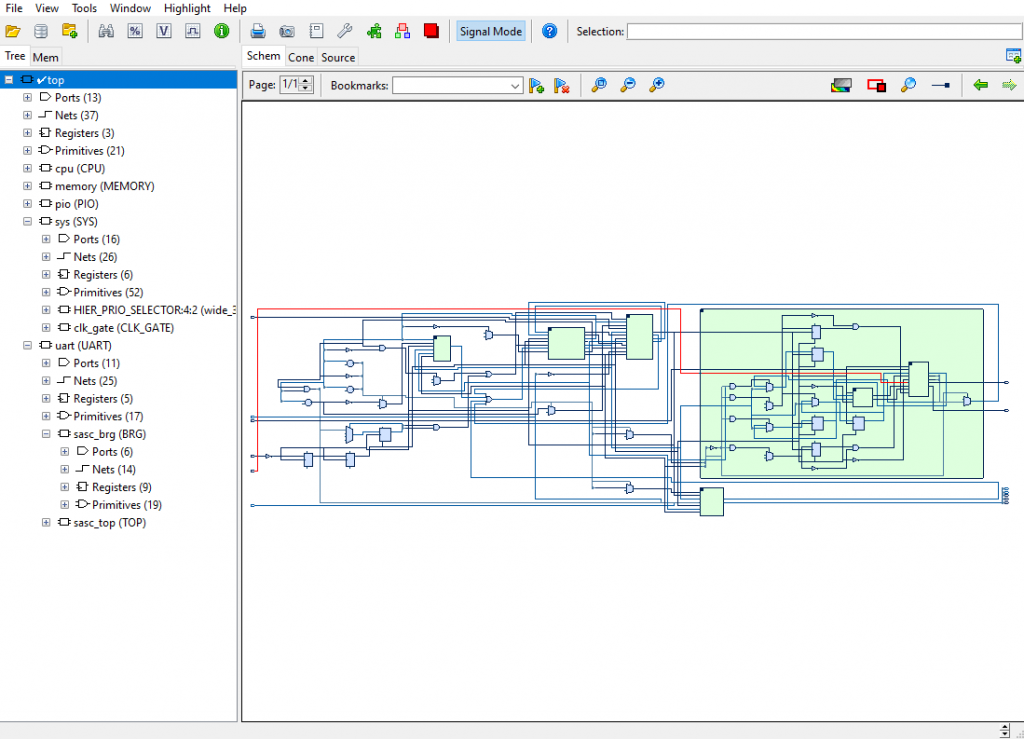

We will show how interactive schematic visualization, extracted path views of incremental schematic, & DRCs can help you with debugging various forms of RTL, SOCs, IPs, netlists and FPGAs and assist in speeding up verification time.

What you will learn:

Visualize: Quickly import 100s of Verilog/SV, VHDL files & render schematics on the fly for any form of RTL of GATE netlist, to understand the functionality of design easily. Visualize in both detailed & abstract block level views.

Logic tracing: Do design exploration with incremental schematic view, quickly extract path between any two points, find all clk outputs and display, etc.

IP Stitching: Check inputs/outputs visually after integrating IP.

Custom DRCs: Easily develop custom DRCs for design for help in IP Integration, design exploration, and more. Access open API for loaded database.

DFT: During the early stages of chip development when integrating the DFT, get a visual of what the incomplete design looks like before DFT insertion, and what it looks like after DFT insertion.

Visualize DFT tool generated RTL: Visualize a Human readable schematic from generated RTL outputted from DFT tools.

RTL Handoff Flow: Obfuscate parts of RTL design for sending to 3rd party for Synthesis. Explore gate level netlist with annotated STA results from 3rd party without using Synthesis/STA tool & cross probe to RTL.

GATE Netlist Debug: Load gate level netlist & explore, annotate primetime timing data.

Visually compare differences in Gate or RTL netlist: Instead of running long LEC run, view in minutes differences between revisions of designs.

Prune: Extract, navigate and save critical timing paths/fragments of the design as Verilog or EDIF format for reuse as IP or for partial simulation.

Clock Domain Analyzer: Visualize and detect different clock domains in the design.

Document: Generate design statistics & reports: Instance & primitive counts.

Who should attend:

· Digital Design and Verification Engineers / Managers

· CAD Engineers / Managers

· FPGA Engineers

· Front End Engineers

· DFT Engineers

· SOC Integrators

Intel High NA Adoption