The old phrase that the cure is worse than the disease is apropos when discussing MBIST for large SOCs where running many MBIST tests in parallel can exceed power distribution network (PDN) capabilities. Memory Built-In Self-Test (MBIST) usually runs automatically during power on events. Due to the desire to speed up test and chip boot times, these tests are frequently run in parallel. The problem is that they can easily produce switching activity that is an order of magnitude above the levels found during regular chip operation. Indeed, these higher switching activity levels not only can cause supply droop affecting the test results, but also the high heat generated can harm chips. These effects can lead to incorrect binning or event direct and latent failures.

The solution is to simulate MBIST activity to predict the load on the PDN and the related thermal effects. With simulation results in hand, designers can correctly decide how many and which memory blocks can be tested in parallel. However, this is not always feasible in large SOCs with many memory blocks because the simulation times may be prohibitive. With gate level and even less accurate RTL simulation it may not be possible to run enough cycles to get the information needed.

In a white paper titled “Analyzing the power implications of MBIST usage”, Siemens EDA looks at how designers can run sufficient simulation to make informed decisions on the testing strategy before tapeout. Siemens worked with ARM on one of their test chips to create a test case where they could apply hardware emulation with the DFT and Power apps for the Siemens hardware emulator Veloce. First, the Veloce DFT app is used to output the internal activity during MBIST emulation. The app uses the Standard Test Interface Language (STIL) and produces industry standard output files.

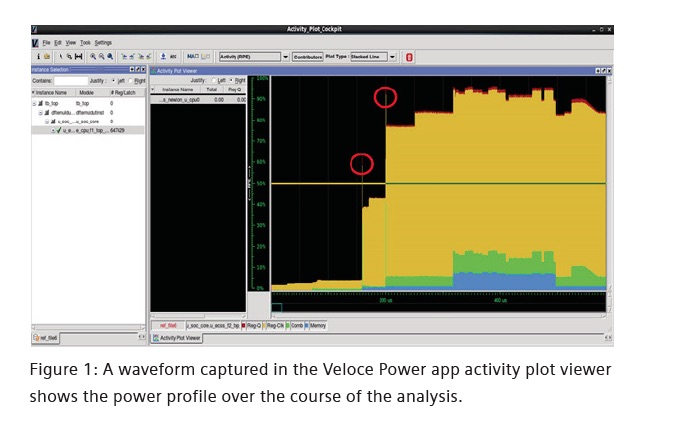

The Veloce Power app takes the activity information from the MBIST runs to generate waveforms, power profiles and heat maps that can indicate when there are power spikes above specified limits. With this information test engineers can make informed decisions about the sequencing of MBIST.

The ARM test case described in the Siemens white paper contains 176 million gates. Siemens used a Veloce system with 6 Veloce Strato boards for this test case. The Veloce emulator run took only 26 hours, which is 15,600 times faster than gate level simulation. Another benefit of the Veloce flow is that the activity information is streamed by the Power app to the power tools in the flow, saving disk space and time. The results from the test case showed several power spikes that violated the SOC design specifications. The output from the Veloce Power app shows the total power levels through the simulation along with the separate power contributions for the clock, combinational logic and memory. Likewise, there is information on where on the die the power is being used. This information makes it easy to determine where there are problems.

Finding problems such these requires running millions or billions of clock cycles. The limitations of software simulators make it prohibitive to perform the necessary analysis. Emulation offers a unique avenue to closely examine the power impacts of MBIST and other test operations long before silicon. The Siemens white paper offers insight into the power method used on a real test case. The white paper is available to download for reading on the Siemens website.

Also Read:

From Now to 2025 – Changes in Store for Hardware-Assisted Verification

DAC 2021 – Taming Process Variability in Semiconductor IP

DAC 2021 – Siemens EDA talks about using the Cloud

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.