In the early days of Atrenta I met with Ralph Marlett, a distinguished test expert with many years of experience at Zuken and Recal Redac. He talked me into believing we could do meaningful static analysis for DFT-friendliness at RTL. His work with us really opened my eyes to the challenges that test groups face in integrating their highly complex additions into the mission mode RTL developed by the mainstream design group. Test is generally an independent team tasked with finding and working around test challenges in each new RTL drop. Typically in crazy short schedule allowances. One of those challenges that doesn’t get a lot of attention is the intersection between power management and test. Defacto has added power in test analytics to their tool suite in support of this need.

Why care about power in test?

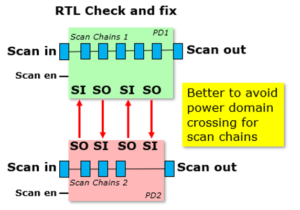

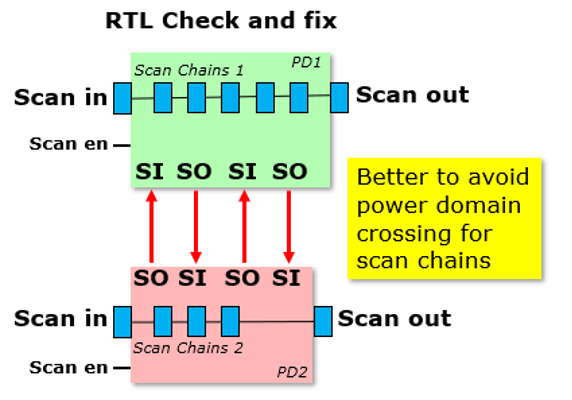

Power-managed SoCs are typically designed with the assumption that they will never be on everywhere and clocking everywhere across the chip. That would be crazy – they would burn out right? But what about when the die/wafer is on a tester? Speed of test is paramount, so the default testing mode works directly against that power assumption. This means that test now also needs to become power aware. Scan chains have to understand power and DVFS domains for example. They have to be grouped in ways that are consistent with UPF-defined domains. For example, recognizing that scan chains running between different domains may require them to conflict with mean or peak power plans.

Equally domain-switching signals must be accessible from the testing environment. Usually we think of the power state engine managing these exclusively (in turn also managed by software). But test needs a more direct handle on these controls. And of course test signals crossing between voltage domains need UPF commands for level shifters.

Automating test feasibility, adaptation

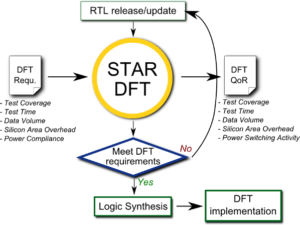

This stuff is all routine these days in mission mode RTL development, but test teams have expertise in test, not so much in power management, so they welcome help in navigating these new requirements. Defacto have stepped in to help test experts model the interaction between their test plans and the power architecture. Through the STAR platform, a test expert can stitch trial scan chains and trial power control overrides (in test mode) into the RTL. This after all is what Defacto do really well, incrementally modifying RTL to stitch in nets and instances. They can visualize how chains overlap power domains and how domain control signals interact with those domains. They can also auto-fix such cases.

A test engineer can model how all of this interacts with test compression for what-if analysis, varying the number of EDT channels and scan chains. Based on this, the Defacto flow will allow them to assess compression-aware test coverage estimates. They can dump that modified RTL, along with a testbench to drive scan testing. Which they can they run in their favorite simulator to validate test functionality.

Defacto got their start in helping test engineers stitch test logic into design RTL, so this is a very natural advance for them to add, especially since the test experts already know and depend on their tools. You can learn more about Defacto here and you can see them at virtual ITC 2020 November 3rd-5th.

Also Read

Atos Crafts NoC, Pad Ring, More Using Defacto

Build Custom SoC Assembly Platforms

Another Application of Automated RTL Editing

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.