Siemens has strengthened its position in EDA and manufacturing by acquiring ASTER Technologies, a specialist in test and reliability solutions for printed circuit boards. The acquisition represents a strategic step in Siemens’ broader vision to deliver a fully integrated, end-to-end digital thread for electronics design,… Read More

Tag: dft

Addressing Silent Data Corruption (SDC) with In-System Embedded Deterministic Testing

Silent Data Corruption (SDC) represents a critical challenge in modern semiconductor design, particularly in high-performance computing environments like AI data centers. As highlighted in a collaborative presentation by Broadcom Inc. and Siemens EDA at the 2025 TSMC OIP event, SDC occurs when hardware defects cause erroneous… Read More

Propelling DFT to New Levels of Coverage

Siemens recently released a white paper on a methodology to enhance test coverage for designs with tight DPPM requirements. I confess when I first skimmed the paper, I thought this was another spin on fault simulation for ASIL A-D qualification, but I was corrected and now agree that while there are some conceptual similarities… Read More

Easy-Logic and Functional ECOs at #61DAC

I first visited Easy-Logic at DAC in 2023, so it was time to meet them again at #61DAC in San Francisco to find out what’s new this year. Steven Chen, VP Sales for North America and Asia met with me in their booth for an update briefing. Steven has been with Easy-Logic for six years now and earned an MBA from Baruch College in New York. This… Read More

Upskill Your Smart Soldiers and Conquer the Chip War in Style!

My recent article, ‘Chip War without Soldiers’ explained the importance of upskilling and preparing the chip design workforce in this current scenario, and it also explained how it will lead to ‘Fabs without Chips’ if we don’t prioritize it. VLSI Engineers are the pillars of the semiconductor industry, and they can only transform… Read More

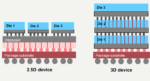

DFT Moves up to 2.5D and 3D IC

The annual ITC event was held the last week of September, and I kept reading all of the news highlights from the EDA vendors, as the time spent on the tester can be a major cost and the value to catching defective chips from reaching production is so critical. Chiplets, 2.5D and 3D IC design have caught the attention of the test world, … Read More

CEO Interview: Sivakumar P R of Maven Silicon

Sivakumar P R is the Founder and CEO of Maven Silicon. He is responsible for the company’s vision, overall strategy, business, and technology. He is also the Founder and CEO of Aceic Design Technologies.

Sivakumar is a seasoned engineering professional who has worked in various fields, including electrical engineering,… Read More

Smarter Product Lifecycle Management for Semiconductors

Product Lifecycle Management (PLM) for electronic systems has moved from a passive ‘fire and forget’ approach to one that is intimately involved not only during design, but also throughout the entire life of every unit delivered to the field. Siemens EDA has a white paper titled “Tessent Silicon Lifecycle Solutions” that talks… Read More

Observation Scan Solves ISO 26262 In-System Test Issues

Automotive electronic content has been growing at an accelerating pace, along with a shift from infotainment toward mission critical functions such as traction control, safety systems, engine control, autonomous driving, etc. The ISO 26262 automotive electronics safety standard evolved to help ensure that these systems… Read More

Mentor Offers Next Generation DFT with Streaming Scan Network

Design for test (DFT) requires a lot of up-front planning that can be difficult to alter if testing needs or performance differ from initial expectations. Hierarchical methodologies help in many ways including making it easier to reduce on chip resources such as the number of test signals. Also, hierarchical test allows for speed-ups… Read More