Standards help our EDA and IP industry grow more quickly and with less CAD integration efforts, and IP-XACT is another one of those Accellera standards (1685-2009) that is coming of age, and enabling IP reuse for SoC design teams. Here at SemiWik, we’ve been writing about Defacto Technologies and their prominent use of IP-XACT since 2016. I just learned about a new webinar from Defacto, planned for November 10th at 10:00AM PST.

Challenges

With any complex standard it can take awhile to develop an efficient methodology for SoC design, and it’s expected that in 2021 we’ll see a new standard version emerge. Having compliance with an RTL implementation flow can be rather painful and not obvious for first-time designers.

Webinar Overview

Today, an increased number of IPs are delivered using IP-XACT interfaces which should ease the integration process. However, it is still a complex format to handle and not every company (or designer) wants to jump into a new format. The tight relationship between the standard and RTL will be highlighted in the webinar, along with using more automation to keep them correlated. Both system level and RTL designers are going to benefit from attending the webinar.

We observe several categories of users and reactions around IP-XACT:

- Those who are already using IP-XACT but would like to have the design information fully compliant with an RTL design flow

- Those who want to adopt this standard with full compliance with RTL design flow but are a bit reluctant knowing the format complexity.

- Those who want to avoid using IP-XACT as much as possible

Defacto’s SoC Compiler addresses users above and helps building a unified and IP-XACT and RTL design flow. During this webinar Defacto’s SoC Compiler 9.0 key capabilities will be illustrated through typical cases such as:

- Extraction of design information

- Coherency checks between IP-XACT, RTL, UPF and SDC

- IP-XACT <-> RTL view generation

- Joint IP-XACT & RTL Integration

- System level handling and report with a focus on memory map.

SoC Compiler

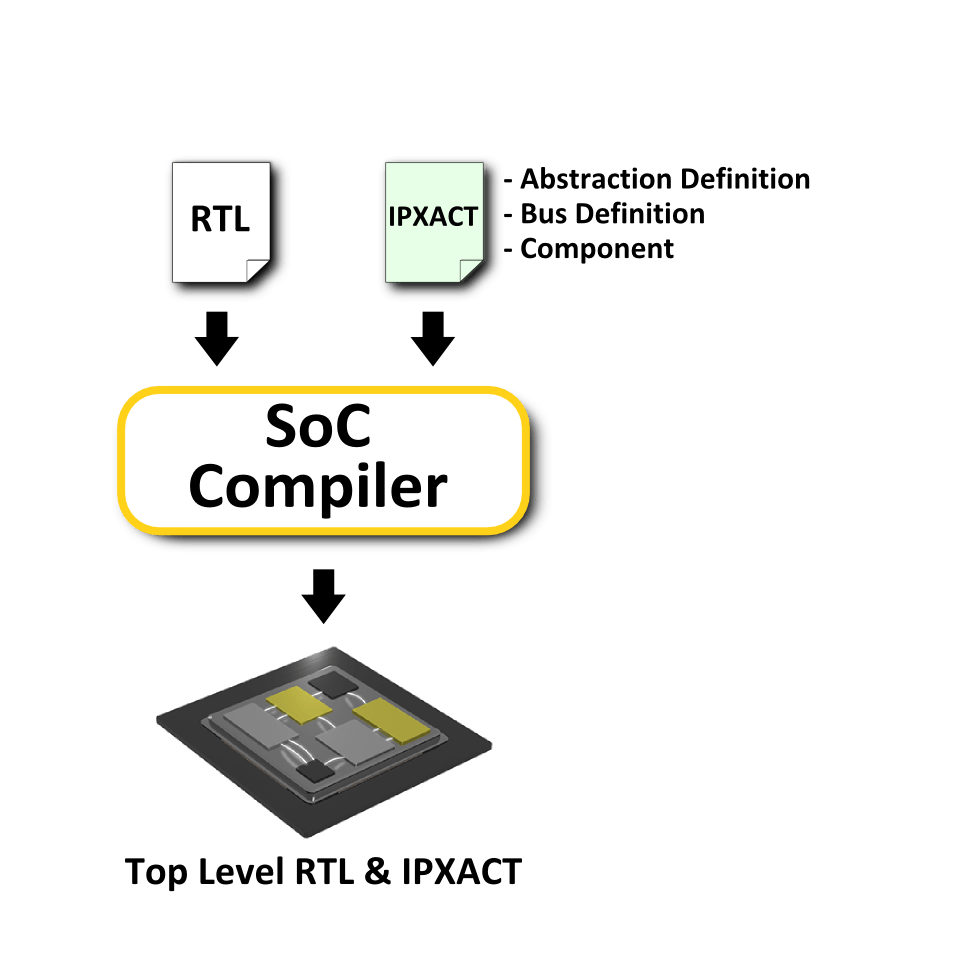

SoC Compiler provides unique capabilities to build a complete SoC at RTL with all the mechanisms to edit the design and deliver a correct-by-construction RTL and the associated views such as SDC and UPF, ready for synthesis.

SoC Compiler enables the SoC design assembly process with full support of IP-XACT standard in full compliance with RTL files. Several automated design “extraction, packaging and reuse” capabilities are provided. Defacto is part of the Accellera committee for the definition of IP-XACT standard and an active member of the IP-XACT 2021 version

Summary

During the webinar, attendees will get a clear picture of how SoC Compiler helps to build a cost-effective and robust flow to manager IP-XACT complexity. Register for the REPLAY here.

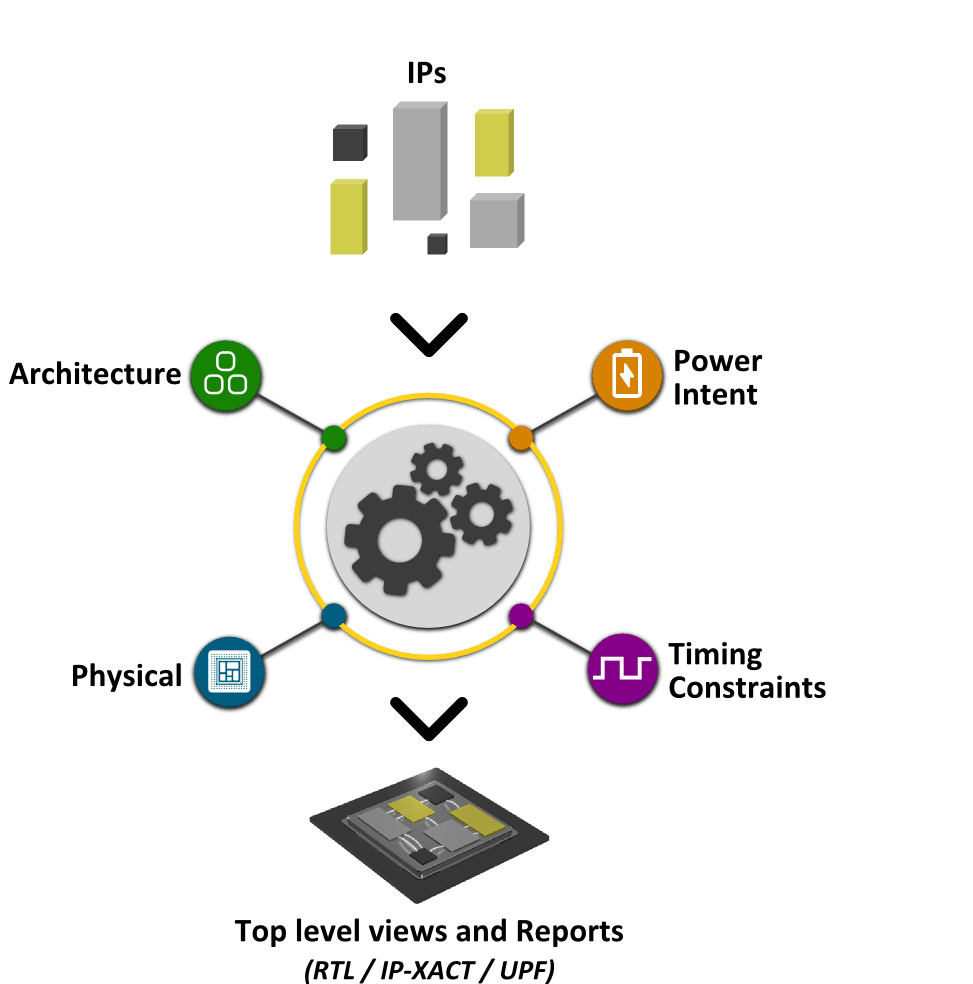

Defacto Technologies is a leading provider of RTL design solutions which help users to build a unified design flow where different standards like RTL, IP-XACT, UPF for power intent, SDC for timing constraints, LEF/DEF for physical design information, are considered. Defacto SoC Compiler is a silicon proven EDA solution which are helping major semiconductor companies to add automation to their design flows mainly at RTL and enhance integration, verification and Signoff of IP cores and System on Chips.

Related Blogs

- WEBINAR: What Makes SoC Compiler The Shortest Path from SoC Design Specification to Logic Synthesis?

- Small EDA Company with Something New: SoC Compiler

- CEO Interview: Dr. Chouki Aktouf of Defacto

- Power in Test at RTL Defacto Shows the Way

- Atos Crafts NoC, Pad Ring, More Using Defacto

- Build Custom SoC Assembly Platforms

Comments

There are no comments yet.

You must register or log in to view/post comments.