Modern SoCs can be complex with hundreds to thousands of IP blocks, so there’s an increasing need to have a front-end build and assembly methodology in place, eliminating manual steps and error-prone approaches. I’ve been writing about an EDA company that focuses on this area for design automation, Defacto Technologies, and … Read More

Tag: sdc

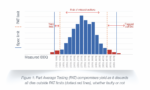

Cut Defects, Not Yield: Outlier Detection with ML Precision

How much perfectly good silicon is being discarded in the quest for reliability? During high-volume chip manufacturing, aggressive testing with strict thresholds may ensure quality but reduces yield, discarding marginal chips that could function flawlessly. On the other hand, prioritizing yield risks allowing defective… Read More

Enhancing System Reliability with Digital Twins and Silicon Lifecycle Management (SLM)

As industries become more reliant on advanced technologies, the importance of ensuring the reliability and longevity of critical systems grows. Failures in components, whether in autonomous vehicles, high performance computing (HPC), healthcare devices, or industrial automation, can have far-reaching consequences.… Read More

Webinar – How to manage IP-XACT complexity in conjunction with RTL implementation flow

Standards help our EDA and IP industry grow more quickly and with less CAD integration efforts, and IP-XACT is another one of those Accellera standards (1685-2009) that is coming of age, and enabling IP reuse for SoC design teams. Here at SemiWik, we’ve been writing about Defacto Technologies and their prominent use of IP-XACT… Read More

Small EDA Company with Something New: SoC Compiler

I read the semiconductor press, LinkedIn and social media (Twitter, Facebook) every morning along with an RSS feed that I setup, staying current on everything related to using EDA tools to make the task of SoC design a bit easier for design teams. A recent press release announced a tool called SoC Compiler, so my curiosity was piqued… Read More

A Complete Scalable Solution for IP Signoff

In an SoC world driven by IP, where an SoC can have hundreds of IP (sourced not only from 3[SUP]rd[/SUP] party but also from internal business units which can have a lot of legacy) integrated together, it has become essential to have a comprehensive and standard method to verify and signoff the IP. Additionally, these checks must … Read More

A Complete Timing Constraints Solution – Creation to Signoff

With the unprecedented increase in semiconductor design size and complexity design teams are required to accommodate multiple design constraints such as multiple power domains for low power design, multiple modes of operation, many clocks running, and third party IPs with different SDCs. As a result timing closure has become… Read More

RTL Designers Can Win a GoPro Camera at DAC

DACis just 33 days away and who wouldn’t want a cool GoPro camerato play with? Your manager will certainly want you to first check out what’s new at DAC if your job involves getting to RTL signoff on time and within budget. The creative folks at Atrenta have figured out how to attract us with the offer of winning a GoPro camera,… Read More

Expert Constraint Management Leads to Productivity & Faster Convergence

The SoC designs of today are much more complex than ever in terms of number of clocks, IPs, levels of hierarchies, several modes of operations, different types of validations and checks for growing number of constraints at various stages in the design flow. As a semiconductor design evolves through several stages from RTL to layout,… Read More

Start With The End In Mind – For Complete & Fast Success!

There is always a rush to converge a semiconductor design toward faster closure, amid increasing divergent trends of multiple IPs and high complexities of various functionalities on a single chip. Every design house struggles hard to evolve its customized design flows with several short paths patched up to fix issues, global… Read More