With the increasing on-chip integration capabilities, large scale electronic systems can be integrated into a single System-on-Chip or SoC. New manufacturing test challenges are raised for more advanced technology nodes where both quality and cost during testing are affected. A typical parameter is test coverage which impacts directly yield.

Test point exploration is becoming a key for large system on chip designs especially for automotive & security applications where test coverage figures are expected to reach 99% and more. To reach such high coverage figures, area overhead is usually quite high. EDA tools in general are still conservative and any analysis of “test coverage vs. test logic implementation” requires tedious manual work especially when realized post-synthesis.

In summary, Test Point Exploration & Implementation (TPI&E) is nowadays a key problem for DFT engineers.

Beyond the exploration of different test point figures, the implementation impact of thousands of test points is an important problem to consider the earliest in the design flow. As most of the test logic today such as test compression, self-test, IEEE 1500, etc., it is expected the implementation of test points to occur pre-synthesis at RTL level.

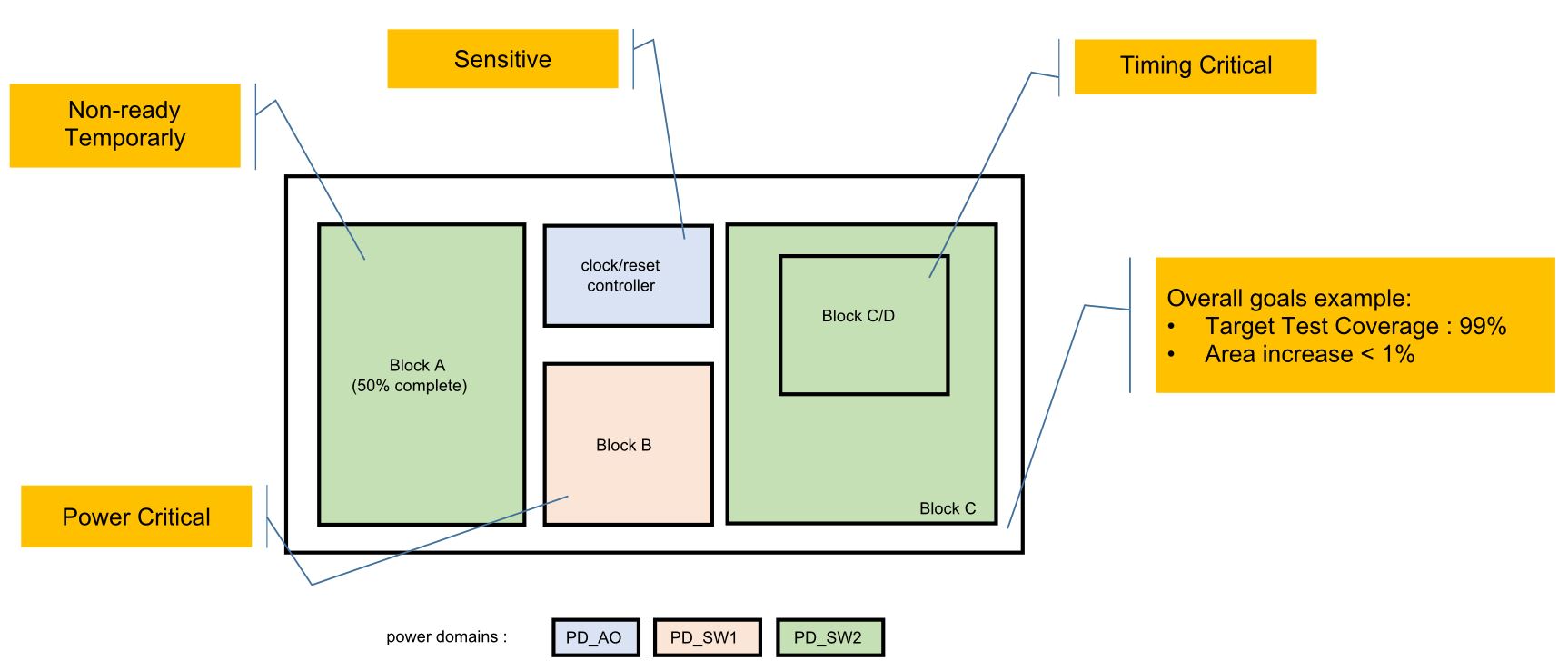

Another important aspect to consider is related to design constraints and design collaterals which should be taken into consideration during the test point exploration and implementation design steps. Typical related questions are: test points should belong to which power domain, to which clock domain, and to which physical partition? Managing design collaterals usually means automated management of the related design data such as UPF, SDC, LEF/DEF, etc.

Finally, beyond the TPI &E process, once test points are implemented at RTL, the impact on the design verification process is key. This includes RTL simulation, netlist elaboration, etc.

Defacto Technologies has been providing EDA DFT solutions for more than 20 years and has recently developed a new methodology to make this test point exploration and implementation process easy and straightforward. The proposed EDA TPI&E solution is structured into four steps:

Step 1: Capture user requirements and constraints

The idea here is to provide DFT engineers with the ability to introduce the expected test coverage and the afforded cost (area overhead) with different design constraints. Typical examples of constraints can be for test points which need to be excluded from certain scan chains or those which should not be part of timing critical paths., etc.

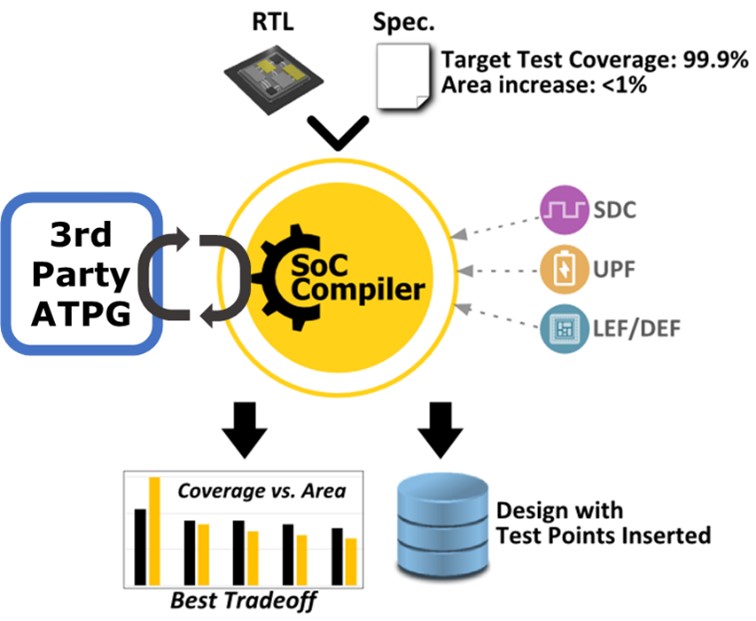

Step 2: Explore ATPG test points configuration as soon as at RTL!

Knowing that the exploration and insertion run pre-synthesis, Defacto tools fully support an automated ATPG-based RTL analysis. For mainstream ATPGs, here the goal is to benefit from the ATPG-based list of test points and help explore their efficiency as soon as at RTL. Design constraints from SDC, UPF, LEF/DEF or similar formats, are easily considered as part of the test points exploration process.

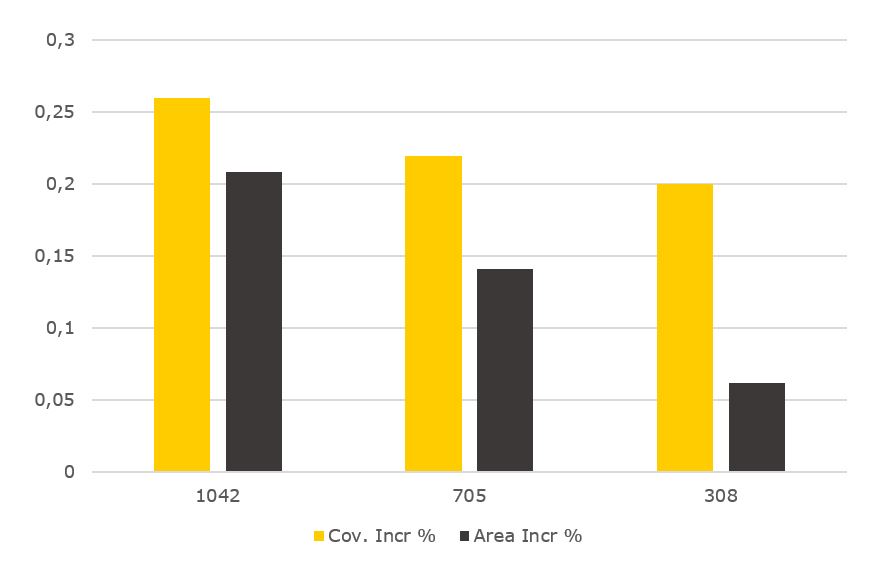

Step 3: for the list of TPI configurations that are suggested by the ATPG, measure the quality of the list of test points and the related cost through the generated coverage/area reports.

At a glance, the most optimal test point configuration with the best trade-off is obtained.

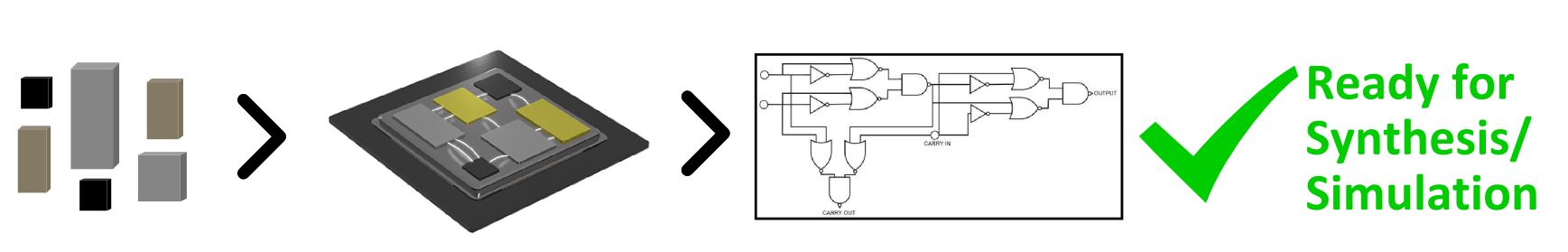

Step 4: Once the most optimal configuration is selected, inserted test points are implemented at RTL and the final SoC top level RTL files are generated, ready for both logic synthesis and design verification processes.

Step 5: Run DFT verification tasks at RTL including the RTL simulation of ATPG vectors, testability design rule checks, linting, etc. in full compliance with design collaterals.

The above process and steps with fully automated test point exploration, implementation, and verification capabilities are part of Defacto’s SoC Compiler V10. This flow was shown to be efficient in checking and fixing test point related problems for large IPs, subsystems and SoCs. It has been used by several major semiconductor companies to quickly obtain a significant coverage improvement with a moderate area increase.

Worth mentioning that this solution is vendor agnostic and fully interoperates with mainstream DFT implementation flows. As a result, the overall DFT throughput is drastically improved as soon as at RTL. The obtained experiments clearly show the potential of this unique DFT flow to help face the key DFT challenges.

Defacto Team will be attending the International Test Conference in Anaheim on October 9th to present this Test Point Exploration & Implementation Solution. Feel free to contact them to request a meeting, a demo, or an evaluation: info_req@defactotech.com.

Also Read:

Defacto Celebrates 20th Anniversary @ DAC 2023!

Defacto’s SoC Compiler 10.0 is Making the SoC Building Process So Easy

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.