Historically, the semiconductor and semiconductor equipment industry were inextricably linked due to the cyclical nature of the chip industry. An increase in semiconductor revenues was followed within a short period with an increase in equipment revenues, as semiconductor companies purchased equipment to make more chips… Read More

AMAT and the Jinhua Jinx!

Applied Materials reported a just “in line” quarter but guidance was well below street expectation. AMAT reported EPS of $0.97 and revenues of $4.01B versus street of $0.97 and $4B. Guidance missed the mark by a wide margin with revs of $3.56 to $3.86 and EPS of $0.75 to $0.83 versus already reduced street expectations… Read More

Open-Silicon Embraces the Latest ISO 9001 Specification with Certification by SGS

A quality standard that stays static and is not itself targeted for continuous improvement, is a standard that is breaking one of the first tenets of quality. This is why the ISO 9001 specification has been updated several times since its introduction in 1987. The first version was fairly modest. The most recent version was released… Read More

Home Automation IoT Company Cuts ASIC Testing Costs

Customer Case Study

digitalSTROM develops smart home automation solutions providing users with superior comfort and a whole new style of living. Based on proprietary ASIC and software, digitalSTROM’s solutions connect electrical household appliances through existing power lines and enable an intelligent home via light… Read More

Q4 Hiring remains strong Outlook for Q1 2019

Things are going quite well in the Valley, ESPECIALLY if traffic is any indication. I still remember the BUST with the empty office buildings and light traffic, back in the early 2000’s…while I wish for traffic like that always, I certainly prefer the busy times, guess you cannot have it all. The more traffic, the more jobs; they invariably… Read More

UMC the Next China Chip Embargo?

The DOJ last week released a previously sealed indictment against UMC, Jinhua and three individuals for stealing Micron trade secrets. The indictment is very damning of UMC with very specific semiconductor technology files that were stolen by UMC related people then passed on to Jinhua through its joint development with UMC.… Read More

Playing the Long Game with 56G SerDes

IP has always been a hot topic on SemiWiki with quite a bit of our readers doing the “make versus buy” analysis. SerDes is one of the more difficult “makes” so it is mostly a “buy” analysis made by networking class ASIC architects and a handful of other applications that demand high performance and throughput. Based on the recent traffic… Read More

Semiconductor stocks free fall as bad news gets worse

Semiconductor stocks have had another significant down leg as the bad news continues to pile on. Bad news in this case doesn’t come in threes , it comes in droves. TI is perhaps very scary news as it is a rather broad based supplier of semiconductors that has fared better than more pure play chip suppliers. TI gave weak guidance… Read More

ASML most immune to slow down due to lead times Not LRCX

ASML reported EUR2.78B in revenues with EUR2.08B in systems. 58% was for memory. EUV was EUR513M with 5 systems. Importantly orders were for EUR2.20B in systems at 64% memory and 5 EUV tools. This was likely better than expectations given the overall industry weakness. EPS of EUR1.60 was more or less in line with expectations. Guidance… Read More

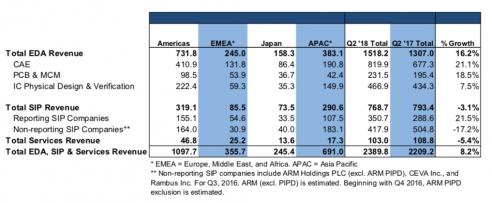

Who is Responsible for SIP Revenue Decline in Q2 2018?

According with ESDA, EDA revenues have grown YoY by 16.2% in Q2 2018, and this is the good news for our industry. The bad news is the decline of SIP (Design IP) revenues, by (3.1%) at the same time. As far as I am concerned, this figure looks weird, so I will try to understand the reason why SIP category can go wrong in a healthy EDA market,… Read More

Solving the EDA tool fragmentation crisis