You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 386

[name] => Semiconductor Services

[slug] => semiconductor-services

[term_group] => 0

[term_taxonomy_id] => 386

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 1211

[filter] => raw

[cat_ID] => 386

[category_count] => 1211

[category_description] =>

[cat_name] => Semiconductor Services

[category_nicename] => semiconductor-services

[category_parent] => 0

[is_post] =>

)

Semiconductor chip package technologies have evolved throughout the years to the point where hundreds of package types are available today.

Most applications will require the more general, single-element packaging for integrated circuits and the other components such as resistors, capacitators, antenna etc. However,… Read More

Every morning I read the headlines from SemiWiki, CNN, LinkedIn and my Twitter feed, and it seems like every week that I read about another security breach that makes me wonder if anything online is secure. Companies try to harden their web sites, IT infrastructure and even their electronic products from being exploited or tampered… Read More

This session will open the DAC IP Track at 10:30 on Monday “How PAM4 and DSP Enable 112G SerDes Design” in Room N264. I am very proud to chair this invited paper session, as it addresses one of the key pieces of design, enabling to exchange data flow at the highest possible data rate. It can be between two chips on the same board, we talk … Read More

Since the beginning of May eSilicon has announced the tape-out of three TSMC 7nm test chips. The first of these, a 7nm 400G Ethernet Gearbox/Retimer design, caught my eye and I followed up with Hugh Durdan, their vice president of strategy and products, to learn more about it. Rather than just respin their 56G SerDes, they decided… Read More

Last week we warned of a further down leg due to China trade. We were surprised how quickly our prediction came true as it appears we are now in the midst of giving back all the upside built in to stocks based on a peaceful resolution of the trade conflict which obviously isn’t happening.

Many of the semi stocks we cover were down… Read More

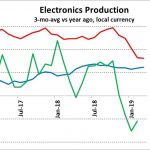

The U.S. is showing steady growth in electronics production. Three-month-average change versus a year ago (3/12) in March 2019 was 6.2%, the 12[SUP]th[/SUP] consecutive month of growth above 5%. China electronics production is decelerating, with March 2019 3/12 growth of 8.2%, similar to 8.3% in February. This marks the first… Read More

We have been very vocal and perhaps the first to warn of the risks to the semiconductor and semiconductor equipment industry from the China trade war with the US. It seems that the war is now fully upon us with the imposition of 25% tariffs by the US and promised retribution by China. The semiconductor industry is at the leading edge … Read More

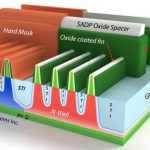

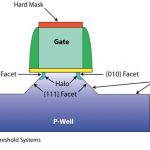

Part 4 of this series discussed how a transistor Extension could be fabricated in a planar device without using an implant operation, and is instead formed using a preferential etch followed by a selective epitaxial deposition. This final installment of the series will present the formation of an Extension in a FinFET transistor… Read More

Perhaps the most innovative and effective Extension implant does not involve an implant at all, but is instead an etch followed by a selective epitaxial deposition.

In this Extension fabrication methodology the Source/Drains regions in a planar device are etched away in the normal fashion to accommodate the replacement Source/Drain… Read More

Just two more weeks before the 2019 CEO Outlook Thursday, May 23, at SEMI. If you haven’t registered yet, do so today. We’re expecting a full house as a result of our powerhouse lineup and networking opportunities.

That lineup includes Ed Sperling, editor in chief of Semiconductor Engineering, who will serve as moderator. Panelists… Read More

Crossing the Yield Cliff: IDP V6 and the Future of Manufacturing Forecasting