It has been an article of faith in the design tools business that there’s little to be gained from targeting market verticals because as far as tools are concerned, all verticals have the same needs. Which is good in some respects; you maximize the breadth of the market to which tooling can appeal. But in so doing the depth of contribution… Read More

FPGA based Prototyping

Webinar: Achieve High-performance and High-throughput with Intel based FPGA Prototyping

FPGAs have been used for ASIC prototyping since the beginning of FPGAs (1980s) allowing hardware and software designers to work in harmony developing, testing, and optimizing their products. We covered the history of FPGAs in Chapter 3 of our book “Fabless: The Transformation of the Semiconductor Industry”, which includes … Read More

FPGA Prototyping Exposed

In case you missed it, the FPGA Prototyping for SoCs webinar happened last week. I did the opening ceremonies which I will run through briefly here or you can go straight to the replay HERE.

FPGA prototyping is one of the fastest growing market segments we track on SemiWiki which brings us to the topic at hand: FPGA Prototyping for SoCs… Read More

Cloud Provider Leverages FPGA Prototyping

Talking to customers is one of the best parts of being a semiconductor professional. It keeps you grounded and offers you the collective experience of some of the smartest people around the world, absolutely.

Webinar: The Emergence of FPGA Prototyping for ASIC/SoC Design

Customer success stories are a close second and interestingly… Read More

Webinar: The Emergence of FPGA Prototyping for ASIC and SoC Design

One of the more interesting markets that I cover is FPGA Prototyping. Interesting because it is fast growing ($150-250M) and interesting because it is all about design starts and design starts are the lifeblood of the semiconductor industry.

If you are interested in FPGA prototyping you might want to start with the 30+ S2C Inc blogs… Read More

Enhancing FPGA Prototype Debug

FPGA prototyping is very popular in modeling hardware for early system prove-out, early embedded software development, as a cost-effective and performance-effective platform for software-driven hardware debug and for late-stage software debug, all before silicon is available. It has significant advantages in run-time… Read More

Blurring Boundaries

I think most of us have come to terms with the need for multiple verification platforms, from virtual prototyping, through static and formal verification, to simulation, emulation and FPGA-based prototyping. The verification problem space is simply too big, in size certainly but also in dynamic range, to be effectively addressed… Read More

Free PDF Version of PROTOTYPICAL for SoC Design

In our quest to further enlighten the masses SemiWiki has published four books, we have two more eBooks in post production due out in Q1 2018 and two more topics in research. All of the books are available free for PDF versions or you can get printed versions on Amazon.com or free printed versions at book signings or if you happen to meet… Read More

Partitioning for Prototypes

I earlier wrote a piece to make you aware of a webinar to be hosted by Aldec on some of their capabilities for partitioning large designs for prototyping. That webinar has now been broadcast and I have provided a link to the recorded version at the end of this piece. The webinar gets into the details of how exactly you would use the software… Read More

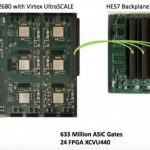

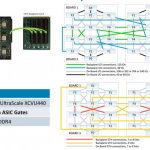

Webinar: Aiding ASIC Design Partitioning for multi-FPGA Prototyping

The advantages of prototyping a hardware design on a FPGA platform are widely recognized, for software development, debug and regression in particular while the ultimate ASIC hardware is still in development. And if your design will fit into a single FPGA, this is not an especially challenging task (as long as you know your way … Read More

Is Intel About to Take Flight?