AI’s rapid expansion is reshaping semiconductor design. The compute and I/O needs of modern AI workloads have outgrown what traditional SoC scaling can deliver. As monolithic dies approach reticle limits, yields drop and costs rise, while analog and I/O circuits gain little from moving to advanced process nodes. To sustain … Read More

Webinar – IP Design Considerations for Real-Time Edge AI Systems

It is well-known that semiconductor growth is driven by AI. That simple statement breaks down into many complex use cases, each with its own requirements and challenges. A webinar will be presented by Synopsys on October 23 that focuses on the specific requirements for one of the most popular use cases – AI at the edge. The speaker… Read More

Why Choose PCIe 5.0 for Power, Performance and Bandwidth at the Edge?

Synopsys recently held a webinar session on this topic and Gustavo Pimentel, Principal Product Marketing Manager at the company led the webinar session. Going into the webinar session, I found myself wondering: why focus on PCIe 5.0, eight years after its release? With the industry buzzing about Edge AI, cloud computing, and … Read More

AI Everywhere in the Chip Lifecycle: Synopsys at AI Infra Summit 2025

At the AI Infra Summit 2025, Synopsys showed how artificial intelligence has become inseparable from the process of creating advanced silicon. The company’s message was clear: AI is an end-to-end engine that drives every phase of chip development. Three Synopsys leaders illustrated this from distinct vantage points. Godwin… Read More

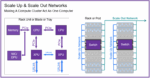

Synopsys Enables AI Advances with UALink

The evolution of hyperscale data center infrastructure to support the processing of trillions of parameters for large language models has created some rather substantial design challenges. These massive processing facilities must scale to hundreds of thousands of accelerators with highly efficient and fast connections.… Read More

448G: Ready or not, here it comes!

The march toward higher-speed networking continues to be guided by the same core objectives as has always been : increase data rates, lower latency, improve reliability, reduce power consumption, and maintain or extend reach while controlling cost. For the next generation of high-speed interconnects, these requirements … Read More

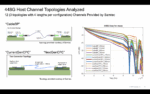

cHBM for AI: Capabilities, Challenges, and Opportunities

AI’s exponential growth is transforming semiconductor design—and memory is now as critical as compute. Multi-die architecture has emerged as the new frontier, and custom High Bandwidth Memory (cHBM) is fast becoming a cornerstone in this evolution. In a panel session at the Synopsys Executive Forum, leaders from AWS, Marvell,… Read More

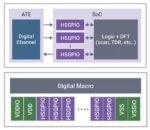

Synopsys Addresses the Test Barrier for Heterogeneous Integration

The trend is clear, AI and HPC is moving to chiplet-based, or heterogenous design to achieve the highest levels of performance, while traditional monolithic system-on-chip (SoC) designs struggle to scale. What is also clear is the road to this new design style is not a smooth one. There are many challenges to overcome. Some are … Read More

Design-Technology Co-Optimization (DTCO) Accelerates Market Readiness of Angstrom-Scale Process Technologies

Design-Technology Co-Optimization (DTCO) has been a foundational concept in semiconductor engineering for years. So, when Synopsys referenced DTCO in their April 2025 press release about enabling Angstrom-scale chip designs on Intel’s 18A and 18A-P process technologies, it may have sounded familiar—almost expected. … Read More

WEBINAR: PCIe 7.0? Understanding Why Now Is the Time to Transition

PCIe is familiar to legions of PC users as a high-performance enabler for expansion slots, especially GPU-based graphics cards and M.2 SSDs. It connects higher-bandwidth networking adapters and niche applications like system expansion chassis in server environments. Each PCIe specification generation has provided a leap… Read More