You might have heard of the Multicore and Multiprocessor SoC (MPSoC) Forum sponsored by IEEE and other industry associations and companies. This group of top-notch academic and industry technical leaders gets together once a year to talk about hardware and software architecture and applications for multicore and multiprocessor… Read More

Semiconductor Intellectual Property

PCIe 6.0 Doubles Speed with New Modulation Technique

PCI-SIG has held to doubling PCIe’s data rate with each revision of the specification. The consortium of 800 companies, with its board consisting of Agilent, AMD, Dell, HP, Intel, Synopsys, NVIDIA, and Qualcomm, is continuing this trend with the PCIe 6.0 specification which calls for a transfer rate of 64 GT/s. PCI-SIG released… Read More

CEO Interview: Dr. Rick Shen of eMemory

Dr. Shen has been President of eMemory Technology since 2009, succeeding Dr. Charles Hsu. Prior to the appointment, Dr. Shen held various management positions within the company, overseeing Technology Development, founding the Customer Service team, supervising Technology & IP services, and the company’s technology… Read More

Adaptive Power/Performance Management for FD-SOI

A vexing chip design issue is how to achieve (or improve) performance and power dissipation targets, allowing for a wide range of manufacturing process variation (P) and dynamic operation voltage and temperature fluctuations (VT). One design method is to analyze the operation across a set of PVT corners, and ensure sufficient… Read More

Arm Announces v9 Generation – Custom, DSP, Security, More

This wasn’t as much of a big bang announcement as others I have seen. More a polishing of earlier-announced reveals, positioning updates, together with some new concepts. First, you probably remember the Cortex-X announcement from about a year ago, allowing users to customize their own instructions into the standard instruction… Read More

5G Calls for New Transceiver Architectures

5G phones are now the top tier devices from many manufactures, and 5G deployment is accelerating in many regions. While 4G/LTE has served us well, 5G is necessary to support next-generation telecommunication needs. It will be used heavily by consumers and industry because it supports many new use cases. There is an excellent white… Read More

Die-to-Die Interface PHY and Controller Subsystem for Next Generation Chiplets

In early April, Gabriele Saucier kicked off Design & Reuse’s IPSoC Silicon Valley 2021 Conference. IPSoC conference as the name suggests is dedicated to semiconductor intellectual property (IP) and IP-based electronic systems. There were a number of excellent presentations at the conference. The presentations had been… Read More

Enabling Next Generation Silicon In Package Products

In early April, Gabriele Saucier kicked off Design & Reuse’s IPSoC Silicon Valley 2021 Conference. IPSoC conference as the name suggests is dedicated to semiconductor intellectual property (IP) and IP-based electronic systems. There were a number of excellent presentations at the conference. The presentations had been… Read More

Low Energy SoCs with Near Threshold Voltage

There is an important difference between low power and low energy in SOC design. Low power focuses on instantaneous power consumption. This is frequently done to deal with cooling and heat dissipation issues. Of course, it serves as a prerequisite for low energy design, which seeks to reduce overall power consumption over time.… Read More

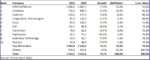

Design IP Sales Grew 16.7% in 2020, Best Growth Rate Ever!

Design IP Sales Grew 16.7% in 2020, to reach $4.6B and this is the best growth since year 2000!

The main trends shaking the Design IP in 2020 are very positive for the Top 3 IP vendors, each of them growing more than the market and confirm the importance of the wired interface IP market, aligned with the data-centric application, hyperscalar,… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center