No matter how impressive the specifications are for an SoC, the power performance and area of the finished design all depend on the IP selected for the IO blocks. In particular, most SOCs designed for consumer and enterprise applications rely heavily on PCI Express. Because PCIe analog IP is critical to design success, Samsung … Read More

Semiconductor Intellectual Property

CEO Interview: Mo Faisal of Movellus

Prior to founding Movellus, Dr. Faisal held positions at semiconductor companies such as Intel and PMC Sierra. Faisal received his B.S. from the University of Waterloo, and his M.S. and Ph.D. from the University of Michigan, and holds several patents. Dr. Faisal was named a “Top 20 Entrepreneur” by the University of Michigan Zell… Read More

High-Performance Natural Language Processing (NLP) in Constrained Embedded Systems

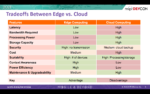

Current technology news is filled with talk of many edge applications moving processing from the cloud to the edge. One of the presentations at the recently concluded Linley Group Fall Processor Conference was about AI moving from the cloud to the edge. Rightly so, there were several sessions dedicated to discussing AI and edge… Read More

Traceability and ISO 26262

Since traceability and its relationship to ISO 26262 may be an unfamiliar topic for many of my readers, I thought it might be useful to spend some time on why this area is important. What is the motivation behind a need for traceability in support of automotive systems development? The classic verification and validation V-diagram… Read More

A MIPI CSI-2/MIPI D-PHY Solution for AI Edge Devices

In late September, the MIPI Alliance held their DevCon conference as a virtual event. There were several excellent presentations at the conference. One of those was titled “A MIPI CSI-2/MIPI D-PHY Solution for AI Edge Devices” by Ashraf Takla of Mixel. Looking at the daily volume of technology news about applications moving to… Read More

Battery Sipping HiFi DSP Offers Always-On Sensor Fusion

Earbuds are one of the fastest growing market segments, which is creating the need for audio DSPs with higher performance and a smaller energy footprint. More than just being wireless speakers – earbuds, and wearables for that matter, have become a sophisticated extension of the user interface of phones and laptops, etc.… Read More

High-Speed Data Converters Accelerating Automotive and 5G Products

While the trend towards System-on-Chip (SoC) has been gathering momentum for quite some time, the primary driver has been integration of digital components, spurred by Moore’s law. Integrating more and more digital circuitry into a single chip has been consistently beneficial for performance, power, form factor and economic… Read More

A Packet-Based Approach for Optimal Neural Network Acceleration

The Linley Group held its Fall Processor Conference 2021 last week. There were a number of very informative talks from various companies updating the audience on the latest research and development work happening in the industry. The presentations were categorized as per their focus, under eight different sessions. The sessions… Read More

Podcast EP46: Arteris IP – the role and impact of system IP

Dan is joined by industry veteran Charlie Janac, chairman, president and CEO of Arteris IP. Dan explores the various products that comprise system IP with Charlie, including the high growth markets he sees. Dan and Charlie also have an interesting discussion about autonomous driving – when and how it will likely be deployed… Read More

CEO Update: Tuomas Hollman, Minima Processor CEO

Tuomas Hollman is an experienced senior executive, with proficiency that ranges from strategy to product development and business management. He began his semiconductor industry career at Texas Instruments, serving for 15 years in increasingly important roles, including general management and profit and loss responsibility… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior