One of my favorite EDA disruptions is the Siemens acquisition of Mentor, pure genius. Joe Sawicki now runs the Mentor IC EDA business for Siemens so we will be seeing him at more conferences and events than ever before. Joe did a very nice keynote at the recent U2U conference that I would like to talk about before we head to the 56thDAC… Read More

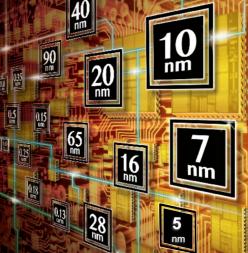

Achieving a Predictable SignOff in 7nm

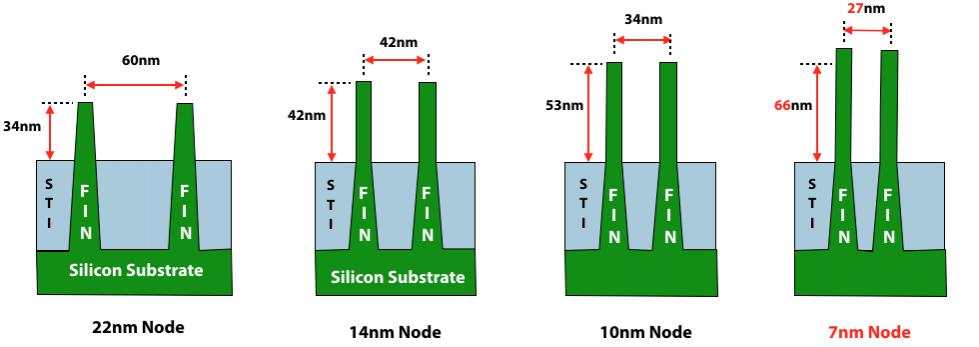

Designing with advanced-nodes FinFETs such as 7nm node involves a more complex process than prior nodes. As secondary physical effects are no longer negligible, the traditional margin-based approach applied at various design abstraction levels is considered ineffective. Coupled with the increase of device counts, failing… Read More

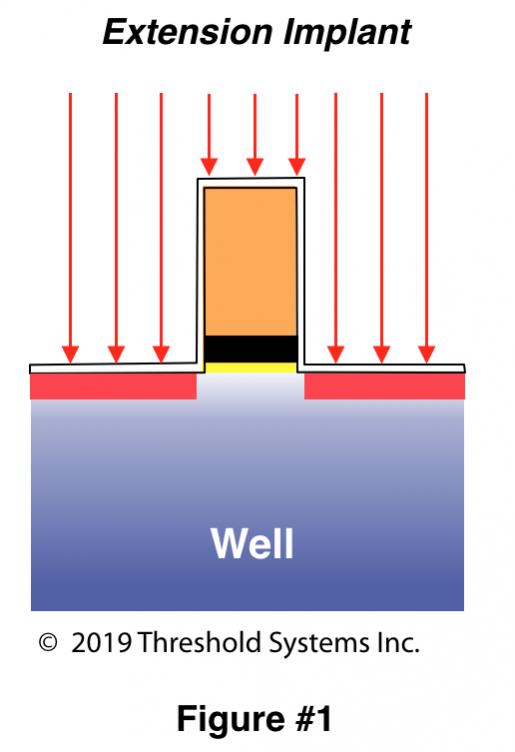

The Evolution of the Extension Implant Part IV

Perhaps the most innovative and effective Extension implant does not involve an implant at all, but is instead an etch followed by a selective epitaxial deposition.

In this Extension fabrication methodology the Source/Drains regions in a planar device are etched away in the normal fashion to accommodate the replacement Source/Drain… Read More

The Evolution of the Extension Implant Part III

The problem of traditional FinFET Extension Implant doping concerns the awkward 3-dimensional structure of the fin. Because the Extension Implant defines the conductive electrical pathway between the Source/Drains and the undoped channel portion of the fin, it is essential that the fin be uniformly doped all three of its surfaces… Read More

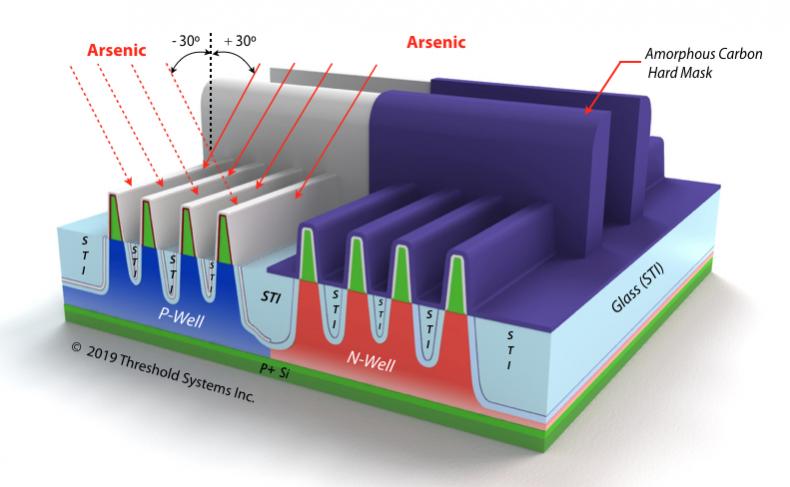

The Evolution of the Extension Implant Part II

The use of hard masks instead of photoresist for the Extension implant is an effective way to optimize the amount of dopant that is retained along the fin sidewalls for those fins that border along photoresist edges (as discussed in Part 1 of this series).

However, hard masks do nothing to address the dominant problem driving steeper… Read More

The Evolution of the Extension Implant Part I

The 3D character of FinFET transistor structures pose a range of unique fabrication problems that can make it challenging to get these devices to yield. This is especially true for the all-important Extension implant that is put in place just prior to the nitride spacer formation.

The Extension implant is a central component of… Read More

A Quick TSMC 2019 Tech Symposium Overview

This year TSMC did a FinFET victory lap with the success of 16nm, 12nm, 10nm, and 7nm. It really is well deserved. Even though TSMC credits the ecosystem and customers, I credit TSMC and their relationship with Apple since it has pushed us all much harder than ever before. TSMC CEO C.C. Wei summed it up nicely in his keynote: Innovation,… Read More

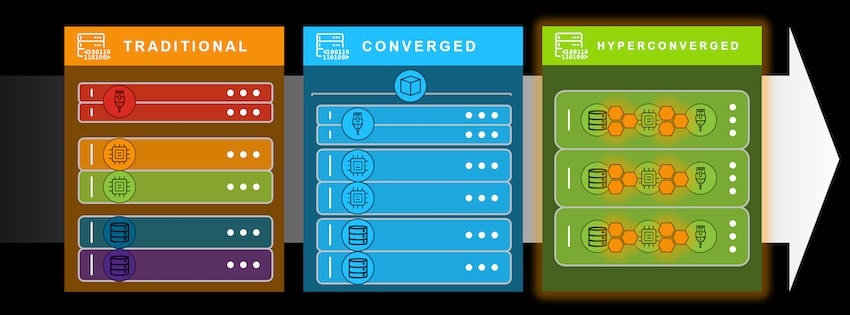

IC Implementation Improved by Hyperconvergence of Tools

Physical IC design is a time consuming and error prone process that begs for automation in the form of clever EDA tools that understand the inter-relationships between logic synthesis, IC layout, test and sign-off analysis. There’s even an annual conference called ISPD – International Symposium on Physical Design… Read More

Samsung 5nm and TSMC 6nm Update

TSMC and Samsung continue to raise the competitive bar for FinFET foundry market share with dueling announcements this week. As I mentioned previously in the blog Semiconductor Foundry Landscape Update 2019, FinFETs are the market to watch with the coming onslaught of 5G and AI chips on the edge, in the cloud, and in our autonomous… Read More

A Collaborative Driven Solution

Last week TSMC announced the availability of its complete 5nm design infrastructure that enables SoC designers to implement advanced mobile and high-performance computing applications for the emerging 5G and AI driven markets. This fifth generation 3D FinFET design infrastructure includes technology files, PDKs (Process… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era