You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 50

[name] => Events

[slug] => events

[term_group] => 0

[term_taxonomy_id] => 50

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 1517

[filter] => raw

[cat_ID] => 50

[category_count] => 1517

[category_description] =>

[cat_name] => Events

[category_nicename] => events

[category_parent] => 0

[is_post] =>

)

Recently, TSMC held their 26th annual Technology Symposium, which was conducted virtually for the first time. This article is the second of three that attempts to summarize the highlights of the presentations. This article focuses on the TSMC advanced packaging technology roadmap, as described by Doug Yu, VP, R&D.

Key… Read More

Designers spend plenty of time analyzing the effects of process, voltage and temperature. But everyone knows it’s not enough to simply stop there. Operating environments are tough and have lots of limitations, especially when it comes to power consumption and thermal issues. Thermal protection and even over-voltage protections… Read More

This is another installment covering TSMC’s very popular Open Innovation Platform event (OIP), held on August 25. This event presents a diverse and high-impact series of presentations describing how TSMC’s vast ecosystem collaborates with each other and with TSMC. This presentation is from Alchip, presented by James Huang,… Read More

Recently, TSMC held their 26th annual Technology Symposium, which was conducted virtually for the first time. This article is the first of three that attempts to summarize the highlights of the presentations.

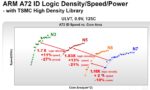

This article focuses on the TSMC process technology roadmap, as described by the following executives:

…

Read More

This is another installment covering TSMC’s very popular Open Innovation Platform event (OIP), held on August 25. This event presents a diverse and high-impact series of presentations describing how TSMC’s vast ecosystem collaborates with each other and with TSMC. The topic at hand was full of superlatives, which isn’t surprising… Read More

After spending a significant amount of my career in the IP library business it was an easy transition to Solido Design. I spent 10+ years traveling the world with CEO Amit Gupta working with the foundries and their top customers. In fact, the top 40 semiconductor companies use Solido. IP companies are also big Solido users including… Read More

FPGAs are a popular method to implement hardware accelerators for applications such as AI/ML, SmartNICs and storage acceleration. PCIe Gen5 is a high bandwidth communication protocol that is a key enabler for this class of applications. Putting all this together presents significant demands on the FPGA for performance and … Read More

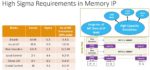

Looking at a typical SoC design today it’s likely to contain a massive amount of memory IP, like: RAM, ROM, register files. Keeping memory close to the CPU makes sense for the lowest latency and highest performance metrics, but what about process variations affecting the memory operation? At the recent DAC conference held… Read More

Similar to my last post on the HCL DevOps webinar series, I will cover their presentation of HCL Compass in a webinar that was recorded on July 29 about how HCL Compass delivers defect tracking and more.

This webinar was presented by Steve Boone, head of product management at HCL Software DevOps, Howie Bernstein, product manager… Read More

The ARC Processor has a rich history. Originally named the Argonaut RISC Processor, it was designed for the Nintendo Game Systems in the 1990s. Argonaut Technologies Limited later became ARC International. My first intimate exposure to ARC was in 2009 when Virage Logic acquired ARC. A year later Virage was acquired by Synopsys… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center