You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4466

[filter] => raw

[cat_ID] => 157

[category_count] => 4466

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

The traditional batch-oriented DRC process run as a final check to ensure compliance with foundry yield goals is quickly moving toward a concurrent DRC process performed early and often throughout design, especially at the 28 nm and smaller process nodes. What are the technology factors causing this change?

…

Read More

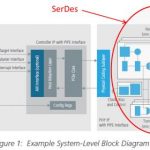

SerDes stands for Serializer/Deserializer, and SerDes is a serious piece of design, requiring an extremely experienced team of analog engineers (below 10 years’ experience, you’re still a quasi-beginner). Better to rely on an analog guru to draw the SerDes architecture and manage the team! Why does SerDes is becoming more and… Read More

Last week I was traveling in Munich attending the MunEDA User Group meetingso I missed a live webinar on the topic of optimizing for power at RTL. I finally got caught up in my email this week and had time to view this 47 minute webinar, presented by Guillaume Boilletof Atrenta. He recommended using a combination of automatic, semi-automatic… Read More

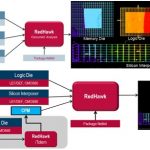

As we move towards packing more and more functionalities and increasing densities of SoCs, the power, thermal and signal integrity issues keep on rising. 3D-IC is a great concept to stack multiple dies on top of each other vertically. While it brings lot of avenues to package dies with multiple functions together, it has challenges… Read More

High-capacity IC place and route (P&R) tools can cost $200K and more to own from the big three vendors (Cadence, Synopsys, Mentor), but what about IC designs that are primarily Big Analog and Little Digital? In the EDA world we often have multiple choices for tools, and there are affordable alternatives to place and route out… Read More

As every other person is talking about IoT today, Michael Munsey of Dassault Systemes looks at this trend in the context of critical success factors and Dassault’s strategy towards providing semiconductor solution that integrates the design chain and continues to keep the semiconductor eco-system healthy and profitable. … Read More

Coverage is an important yet elusive metric for design verification. It often seems 90% of coverage comes with 10% of the effort, and getting the final 10% covered takes the remaining 90% of a project. Usually, it takes another tool or methodology to get at the 10% the first tool missed. With 100% closure difficult, most teams inspect… Read More

IC Design at ZMDIby Daniel Payne on 11-28-2014 at 7:00 pmCategories: EDA, Perforce

As a blogger I have the privilege of meeting many IC designers from around the world, mostly through contact on LinkedIn or from connecting at trade shows. Through a contact at DACI met up with Achim Graupner, a manager of methodology and design automation from ZMDI, then asked him for an interview to understand how his group does … Read More

In today’s electronics with multiple functions working together, heat generation is on the rise; sometimes it becomes intolerable. In fact components running at different temperatures can cause timing issues, and very high temperatures can lead to operational issues such as latch-up. An electronic system can contain chips,… Read More

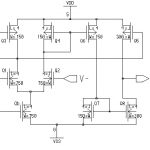

There’s much talk in EDA about High Level Synthesis (HLS), Transaction Level Modeling (TLM) and the Universal Verification Methodology (UVM), however there’s a lower-level of abstraction, the transistor-level, where high-speed digital cell libraries are created, analog circuits are crafted, and AMS designers… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior