With advances in available IP, mixed signal design has become much easier. Mixed signal verification on the other hand is becoming more complicated. More complexity means more simulation, and in the analog domain, SPICE-based techniques grinding away on transistor models take a lot of precious time. Event-driven methods like… Read More

Electronic Design Automation

An Approach to Top-Down SoC Verification

We’ve blogged dozens of times about UVM– Universal Verification Methodology at SemiWiki, and all of the major EDA vendors support UVM, so you may be lulled into thinking that UVM is totally adequate for top-down SoC verification. Yesterday I had a phone discussion with Frank Schirrmeister of Cadence about a new approach… Read More

A Brief History of Silicon Frontline

Silicon Frontline was founded in 2007 by Yuri Feinberg. Since then the company has built up a team with expertise in computational geometry, circuit layout, circuit simulation and analysis, and post-layout verification. After a small initial funding, Silicon Frontline has continued to grow, acquiring new customers even over… Read More

Expert Tool to Easily Debug RTL and Reuse in SoCs

SoC design these days has become a complex and tricky phenomenon involving integration of multiple IPs and legacy RTL code which could be in different languages, sourced from various third parties across the globe. Understanding and reusing RTL code is imperative in SoC integration which needs capable tools that can accommodate… Read More

How are the IoT and ESL Related?

A recent comment by a DACattendee mentioned that the IoT acronym was so over-used as to make him get upset at EDA vendors that all purport to be enabling the growing IoT revolution. One of the most common requirements that I hear about IoT electronics is that the power needs to be well understood and controlled during the design exploration… Read More

Virtual Emulation Extends Debugging Over Physical

Amid burgeoning complexity of SoC verification with ever increasing hardware, software and firmware content, verification engineers are hard pressed with learning multiple tools, technologies and methodologies and still completing SoC verification with full accuracy in time. The complexity, size and diversity of SoC … Read More

Will 3DIC Ever Be Cheap Enough for High Volume Products?

More news from the 3DASIP conference. Chet Palesko of SavanSys Solution had an interesting presentation with the same title as this blog (although this blog draws from several other presentations too). Chet took a look at what aspects of 3D are likely to get cheaper going forward. He took as a starting point that stuff that is not … Read More

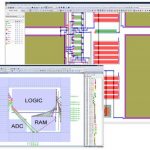

Benefits of Using Schematic Driven Layout

Most IC designs are developed by a team of professionals, often separated into distinct groups like front-end and back-end, logical and physical designers. Circuit designers use tools like schematic capture at the transistor-level to create a topology, then begin simulating the netlist with a SPICE simulator. Layout designers… Read More

A Functional Verification Framework Spanning Simulation to Emulation

Software engineers and firmware designers can find bugs, update their code and re-distribute to the users. In the consumer electronics world this means that my smart phone apps get updated, and my Android OS gets updated on a somewhat regular basis, however on the hardware side the design and verification of an SoC must be close … Read More

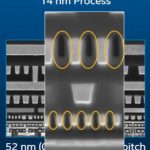

Intel has Another First for 14nm Production!

An interesting thing happened while I was researching a slide from Bill Holt’s “Advancing Moore’s Law” presentation at last month’s analyst meeting. Slide #19 mentioned that Intel was the first to use “air gap” dielectric spaces to improve performance in a digital logic flow for microprocessors. I know a certain foundry that … Read More

Weebit Nano Moves into the Mainstream with Customer Adoption