I visited the Magwel booth at DAC in June and chatted with Dundar Dumlugol the CEO about their EDA tools that enable 3D co-simulation and extraction. Since then I’ve made contact with their CTO, Dr. Wim Schoenmaker to better understand what it’s like to start up and run an EDA company. Magwel’s history goes back… Read More

Electronic Design Automation

Synthesizing rad-tolerant RTL for FPGAs

The maiden voyage of NASA’s Orion spacecraft brought a raft of articles about how the flight computer inside is “no smarter than your phone,” running on wheezing IBM PowerPC 750FX processors. NASA’s deputy manager for Orion avionics, Matt Lemke, admits the configuration is already obsolete – at least in commercial terms. … Read More

Synopsys Q4 Earnings

Synopsys announced their earnings a couple of days ago. This is actually also the end of their fiscal year. They had quarterly earnings of $539M meaning that they did just over $2B for the year. Their guidance for fiscal 2015 is revenue between $2.185B to $2.225B. They said that about 80% of that revenue is already in backlog.

But it… Read More

Variation at IEDM

IEDM (technically the International Electron Devices Meeting although I’ve never heard anyone use the full name) is in a couple of weeks time, in San Francisco. It is December 15-17th at the Hilton Union Square (which is not actually at Union Square but nearby at 333 O’Farrell Street).

For the last few years on the Tuesday… Read More

HLS – Major Improvement through Generations

I am a believer of continuous improvement in anything we do; it’s pleasant to see rapid innovation in technology these days, especially in semiconductor space – technology, design, tools, methodologies… Imagine a 100K gates up to 1M gates design running at a few hundred MHz frequency and at technology node in the range of .18 to … Read More

Design Rule Checking (DRC) Meets New Challenges

The traditional batch-oriented DRC process run as a final check to ensure compliance with foundry yield goals is quickly moving toward a concurrent DRC process performed early and often throughout design, especially at the 28 nm and smaller process nodes. What are the technology factors causing this change?

- Increasing number

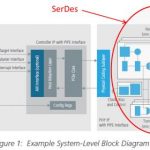

Don’t Mess with SerDes!

SerDes stands for Serializer/Deserializer, and SerDes is a serious piece of design, requiring an extremely experienced team of analog engineers (below 10 years’ experience, you’re still a quasi-beginner). Better to rely on an analog guru to draw the SerDes architecture and manage the team! Why does SerDes is becoming more and… Read More

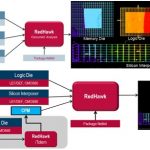

Solution for PI, TI & SI Issues in 3D-ICs

As we move towards packing more and more functionalities and increasing densities of SoCs, the power, thermal and signal integrity issues keep on rising. 3D-IC is a great concept to stack multiple dies on top of each other vertically. While it brings lot of avenues to package dies with multiple functions together, it has challenges… Read More

How to Optimize for Power at RTL

Last week I was traveling in Munich attending the MunEDA User Group meetingso I missed a live webinar on the topic of optimizing for power at RTL. I finally got caught up in my email this week and had time to view this 47 minute webinar, presented by Guillaume Boilletof Atrenta. He recommended using a combination of automatic, semi-automatic… Read More

IC Place and Route for AMS Designs

High-capacity IC place and route (P&R) tools can cost $200K and more to own from the big three vendors (Cadence, Synopsys, Mentor), but what about IC designs that are primarily Big Analog and Little Digital? In the EDA world we often have multiple choices for tools, and there are affordable alternatives to place and route out… Read More

Weebit Nano Moves into the Mainstream with Customer Adoption