You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4440

[filter] => raw

[cat_ID] => 157

[category_count] => 4440

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

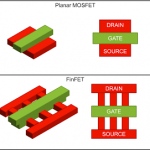

Analog and mixed signal design has received more than their fair share of attention since the mobile revolution and now that FinFETs are in production at the foundries I see that trend continuing. As a result this year there are some interesting things brewing in EDA, especially in the area of Custom Layout.

Innovation in Custom … Read More

IBM is in the process of reinventing themselves as a company, changing how they see themselves, what they do as a company and how they want their partners and customers to view them. This is exemplified best in their mobile alliance with Apple, their Watson cognitive efforts, the sale of their chip fab to GlobalFoundries, the sale… Read More

It has been almost five years since Marc Andreessen wrote the words, “Software is eating the world.” The premise of his essay in the Wall Street Journal in 2011 was pretty simple: the technology world has seen its intrinsic value shift from hardware to software. New all-software names have appeared on the list of high flying companies,… Read More

GPUOpen is a new initiative started by Advanced Micro Devices’ Radeon Technologies Group (RTG) as a way for the company to continue to reach out to the needs to developers by giving them a better development environment. The idea behind GPUOpen is born out of the work that Advanced Micro Device’s did with Mantle, their own low-level… Read More

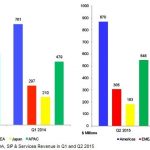

I love reading about good news in the EDA and Semiconductor IP space, especially in light of the recent stock market trending downward in January. The best news that I’ve read in the past week is about the Q3 2015 revenue numbers collected by EDAC, because it shows that Semiconductor IP (SIP) surpassed CAE tool revenues for … Read More

Since Advanced Micro Devices announced their new Radeon Technologies Group (RTG), many have wondered what direction the graphics division would go with its new-found autonomy. The new RTG group within Advanced Micro Devices is still a wholly-owned division of the company but still potentially ripe for acquisition or spinoff.… Read More

The void left by the Advanced Micro Devices X86 server chip “sabbatical” five years ago created a massive opportunity in the server SoC space. It had to be filled with something and that something has primarily been Intel and then ARM-based server chips. ARM Holdings -based servers have been in development for years now and the ecosystem… Read More

If we consider the miniaturization era from year 1963 to 2014 then the computing power of classical computer has increased multi-fold and with the increasing growth in the computing power for every two years the cost per chip has dropped exponentially from few million dollar to few dollars, or even less than dollar per chip. The … Read More

As semiconductor IP is growing bigger in size and more complex in providing complete solution for a particular functionality in an SoC, regions from across the world are joining to provide various types of services in the overall value-chain of IP development, verification, and its integration into SoCs. … Read More

EDA and the Big Short!by Daniel Nenni on 01-05-2016 at 8:00 pmCategories: EDA

A funny thing happened while I was reading “The Big Short: Inside the Doomsday Machine”. The book explains the subprime mortgage crisis in painful detail by profiling several key players who predicted and profited from the bubble pop. As a home owner and faux slumlord I had a front row seat to this horror show so it was an interesting… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center