Portable Stimulus has become such a popular standards topic of late that I thought it would be good to take a break this month from my low power series to bring you, my valued readers, more information about it from one of my colleagues, Dennis Brophy, who is working to help drive development of this standard within Accellera. I’ll … Read More

Electronic Design Automation

How to Gain Low-Power at High-Performance

In a world of smart devices, high performance is required in order to address several specific needs such as intelligent and immediate data processing for IoT applications, instant response from mobile devices, highly interactive user interfaces, and so on. Most of these devices are battery operated and hence require lower … Read More

Mentor takes IoT devices to cloud and back

Walking into the Mentor Graphics booth at ARM TechCon, I was greeted by my friends Warren Kurisu and Shay Benchorin. It was good to see them both again. They were poised in front of a table with a Samsung tablet and a small Wi-Fi-ish box, next to a large Samsung printer. The demonstration was similar to a lobby check-in process, where… Read More

Power Reduction Verification Techniques Highlighted by Mentor at ARM Techcon

Power management is a perennial topic these days, and it came up in several presentations at the recent ARM Techcon in Santa Clara in mid November. The techniques covered in these talks address dynamic and static power consumption. The IEEE 1801 standard deals with specifying power design intent in Universal Power Format (UPF)… Read More

Networks, Emulation and the Cloud

To fans of Godel, Escher and Bach (the Eternal Golden Braid), there is an appealing self-referential elegance to the idea of verifying a network switch in a cloud-like resource somewhere on the corporate network. That elegance quickly evaporates however when you consider the practical realities of verifying such device in ICE… Read More

HLS with ARM and FPGA Technologies Boosts SoC Performance

The way SoC size and complexity are increasing; new ways of development and verification are also evolving with innovative automated tools and environment for SoC development and optimization. IP based SoC development methodology has proved to be the most efficient for large SoCs. This needs collaboration among multiple players… Read More

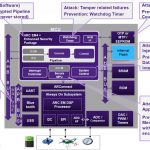

How to Secure IoT Edge Device from Multiple Attacks?

In the 1990’s, designing for performance was the main challenge and the marketing message for Intel processors was limited to the core frequency. Then designers had to optimize power consumption to target mobile phones/smartphone and build power efficient SoC, low power but high performance devices. Now in 2015 the semi industry… Read More

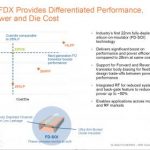

Globalfoundries 22FDX Technology Shows Advantages in PPA over 28nm Node

I really enjoy ARM Techcon when it rolls around every year because it has such a wide range of topics and exhibits. You can find maker gadgets, IoT information, small boards for industrial control, software development kits, semiconductor IP vendors as well as the big EDA players and foundries. This year after perusing the exhibit… Read More

Breaking the Limits of SoC Prototyping

Earlier this month during my conversation with Dr. Walden C. Rhines, he emphasised the need for our next generation designers to think at system level and design everything keeping the system’s view in mind. The verification will go through major transformation at the system level. I can see the FPGA prototyping systems already… Read More

The EDAC Wally Rhines Roast (video)

Last week was the EDAC Phil Kaufman award dinner. It was much more like a roast, probably because Wally has a great sense of humor and as Aart de Geus said, “Wally is a cool cat to have a beer with…” Aart is right of course, hanging with Wally is one of my favorite work things to do.

The place was lousy with media people so I will try and add some… Read More

Intel’s Pearl Harbor Moment