Many years ago, there were attempts to (re-) introduce a graphical entry approach to building RTL design. The Renoir product was one example. The idea has some initial appeal. You describe the behavior in a small block using (textual) RTL but the larger structure of instances and higher-level connectivity can be described as a … Read More

Electronic Design Automation

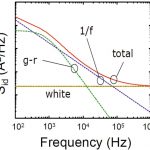

Low Frequency Noise Challenges IC Designs

AMS and RF IC designers have known for years that their circuits are sensitive to noise, because if you amplify noise on an input source to an amplifier circuit then your chip can start to produce wrong answers. Even digital SoC designers need to start taking notice because every SoC is filled with SRAM IP blocks, and at each shrinking… Read More

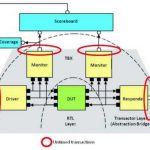

Striving for one code base in accelerated testbenches

Teams buy HDL simulation for best bang for the buck. Teams buy hardware emulation for the speed. We’ve talked previously about SCE-MI transactors as a standardized vehicle to connect the two approaches to get the benefits of both in an accelerated testbench – what else should be accounted for?… Read More

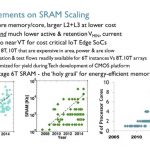

Statistical Simulation Provides Insight into 6T SRAM Optimization

ARM’s Azeez Bhavnagarwala recently gave a talk hosted by Solido on the benefits of variation aware design in optimizing 6T bit cells. Azeez sees higher clock rates, increasing usage of SRAM per processor and the escalating number of processors, shown in the diagram below, as trends that push designers toward 6T. Six Transistor… Read More

The Perfect Wearable SoC…?

Power is Everything

During Apollo 13 after the oxygen tank in the service module exploded forcing the crew to use the lunar module as a life boat to get back home, John Aaron – an incredibly gifted NASA engineer who was tasked with getting the Apollo 13 crew back home safely – flatly stated “Power is everything…we’ve… Read More

Did My FPGA Just Fail?

Designing DRAMs at Intel back in the 1970s I first learned about Soft Errors and the curious effect of higher failure rates of DRAM chips in Denver, Colorado with a higher altitude than Aloha, OR. With the rapid growth of FPGA-based designs in 2016, we are still asking the same questions about the reliability of our chips used for safety-critical… Read More

A New Player in the Functional Verification Space

Israel has a strong pedigree in functional verification. Among others, Verisity (an early contributor to class-based testbench design and constrained random testing) started in Israel and RocketTick (hardware-based simulation acceleration), acquired more recently by Cadence, is based in Israel. So when I hear about an … Read More

More on HAPS hybrid prototyping for ARMv8 with Linaro

A few weeks ago we previewed a Synopsys webinar describing how they are linking the ARM Juno Development Platform with the HAPS-80 and HAPS ProtoCompiler environment. I’ve had a look at the archived event and have some additional thoughts.… Read More

The Package Assembly Design Kit (PADK)… the start of something big

Integrated wafer-level fanout (WLFO) packaging technology is emerging as a foundation for multi-die solutions. Mobile product applications require focus on both aggressive chip-to-chip interface performance, as well as the final package volume. Traditional multi-chip packages using PCB laminate substrates do not readily… Read More

Foundation IP for Automotive: so Stringent Quality Requirements!

The Automotive IC market is not the largest segment, but is certainly the segments expected to grow with the highest CAGR, with 10.8% from 2013 to 2018, according with IC Insights (January 2015). If you consider the pretty long concept/design to production cycle time (7 years or more) as well as the numerous segments just emerging… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center