You can save a lot of power in a design by gating clocks. For much of the time in a complex multi-function design, many (often most) of the clocks are toggling registers whose input values aren’t changing. Which means that those toggles are changing nothing functionally yet they are still burning power. Why not turn off those clock… Read More

Electronic Design Automation

IoT SoCs Demand Good Data Management and Design Collaboration

Design data management has always been important. Board designers have known this for decades as they had to have ways to keep all their discreet components organized and understood. Sourcing components is not easy as it means hours of reading and reviewing specifications, finding reliable sourcing partners and understanding… Read More

Open Silicon Delivers Silicon-Verified HBM2 IP-Subsystem on TSMC 16nm FF+

Open Silicon hosted a webinar today focusing on their High Bandwidth Memory (HBM) IP-subsystem product offering. Their IP-subsystem is based on the HBM2 standard and includes blocks for the memory controller, PHY and high-speed I/Os, all targeted to TSMC 16nm FF+ process. The IP-subsystem supports the full HBM2 standard with… Read More

Improved Memory Design, Characterization and Verification

My IC design career started out with DRAM design, characterization and verification back in the 1970’s, so I vividly recall how much SPICE circuit simulation was involved, and how little automation we had back in the day, so we tended to cobble together our own scripts to help automate the process a bit. With each new process… Read More

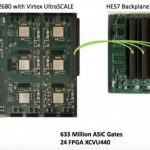

Partitioning for Prototypes

I earlier wrote a piece to make you aware of a webinar to be hosted by Aldec on some of their capabilities for partitioning large designs for prototyping. That webinar has now been broadcast and I have provided a link to the recorded version at the end of this piece. The webinar gets into the details of how exactly you would use the software… Read More

ATopTech is Back!

One of the biggest surprises at the TSMC OIP Forum last week was the reappearance of bankrupt EDA vendor ATopTech. I spoke with former ATopTech CEO and now Avatar IS President Jue-Hsien Chern at OIP. As a survivor of several EDA legal battles myself, I understand what ATopTech went through and I am thoroughly impressed that they had… Read More

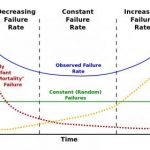

Webinar: Signoff for Thermal, Reliability and More in Advanced FinFET designs

In automotive applications, advanced FinFET processes are great for high levels of integration and low power. But they also present some new challenges in reliability signoff. Ansys will be hosting a webinar to highlight the challenges faced by engineers trying to ensure thermal, electromigration (EM) and electrostatic discharge… Read More

High-Level Synthesis for Automotive SoCs

Some of the world’s most complex Systems-on-Chip (SoCs) are being developed for automotive applications. These SoCs have heterogeneous architectures with a variety of processors and accelerators that do real-time image processing for assisted and autonomous driving applications. The Bosch Visiontec team, in Sophia Antipolis,… Read More

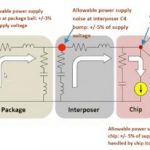

Power Integrity from 3DIC to Board

The semiconductor industry has built decades of success on hyper-integration to increase functionality and performance while also reducing system cost. But the standard way to do this, to jam more and more functionality onto a single die, breaks down when some of the functions you want to integrate are built in different processes.… Read More

Semiconductor Device Physics, Lab in a Box

One of my favorite classes in college was the lab exercise, mostly because we actually got to use real electronics and then measure something, finally writing it up in our lab notebooks. The issue today is that a college student taking Electrical Engineering probably doesn’t have much access to 10nm FinFET silicon for use… Read More

Solving the EDA tool fragmentation crisis