Though hopefully not some of us all of the time. Randomization is a technique used in verification to improve coverage in testing. You develop tests you know you have to run, then you throw randomization on top of that to search around those starter tests, to explore possibilities you haven’t considered. Truly random tests are not… Read More

Electronic Design Automation

Tempus: Delivering Faster Timing Signoff with Optimal PPA

In July, I explored the benefits of the new Cadence Tempus™ Power Integrity Solution. In that piece, I explored some of the unique capabilities of this new tool with Brandon Bautz, senior product management group director and Hitendra Divecha, product management director in the Digital & Signoff Group at Cadence. I recently… Read More

yieldHUB – A Yield Management Checklist for Startups and a New Look

In July, I covered a webinar that described how yieldHUB helps bring a new product to market. That webinar described how to implement new production introduction (NPI) using an array of tools and techniques that should be part of any semiconductor enterprise. In a recent article published by yieldHUB, they took a few steps back … Read More

Digital Design Technology Symposium!

Synopsys virtual events are high on my list for three reasons:

- They are very well organized and professionally

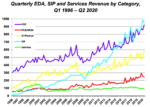

EDA Appears to Have COVID Immunity – ESD Alliance Reports Strong Q2 2020

The ESD Alliance tracks revenue growth for a large number of EDA companies. Their recent report paints a positive picture in a landscape dotted with challenges and not-so-good news. The report cites 12.6% overall revenue growth for Q2 2020 vs. Q2 2019. Furthermore, the overall most recent four quarter revenue average has increased… Read More

CEO Interview: Dean Drako of IC Manage

Dean founded IC Manage in 2003, a company that he has helped expand to become the IC/SoC design and IP management technology leader. Dean was also founder, President and CEO of Barracuda Networks from 2003 to 2012, where he built and expanded Barracuda from a spam and virus firewall provider to a broad line enterprise technology … Read More

SkillCAD Layout Automation Suite has Over 120 Commands Backed by 60 Customers

Cadence Virtuoso is by far the most popular layout tool for IC design. This is especially true at advanced process nodes. In my opinion one of the key reasons for this is its built-in extension language, SKILL. SKILL is a powerful tool to add time saving and customized functionality to the Virtuoso layout editor. For analog and custom… Read More

Siemens PAVE360 Stepping Up to Digital Twins

The idea of a digital twin is simple enough. You use a digital model of a car, aircraft, whatever to test design ideas and prove your design will be robust across a wide range of scenarios before you commit millions of dollars and lives to proving out the real thing. As Siemens have accomplished in their PAVE360 platform. There are a … Read More

Altair HPC Virtual Summit 2020 – The Latest in Enterprise Computing

On September 9 and 10 Altair held their high-performance computing virtual summit. Altair is a company with a large footprint. In their own words, “Altair is a global technology company that provides software and cloud solutions in the areas of data analytics, product development, and high-performance computing (HPC).” Their… Read More

Webinar: Static Verification for RISC-V Cores and SoCs

RISC-V has been trending ever since it landed on SemiWiki in 2016. Even more so now that Arm is in flux with the Nvidia acquisition. Verification is a fast growing EDA challenge with the number of verification engineers steadily outpacing design, so this webinar is a best case scenario for SemiWiki traffic, absolutely.

Two things… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era