Back in my Atrenta days (before mid-2015), we were already running into a lot of very large SoC-level designs – a billion gates or more. At those sizes, full-chip verification of any kind becomes extremely challenging. Memory demand and run-times explode, and verification costs explode also since these runs require access to … Read More

Electronic Design Automation

A Tour of This Year’s DAC IP Track with Randy Fish

DAC is a complex event with many “moving parts”. While the conference has gone virtual this year (as all events have), the depth of the event remains the same. The technical program has always been of top quality, with peer-reviewed papers presented across many topics and across the world. This is also the oldest part of DAC, dating… Read More

Siemens Acquires UltraSoC to Drive Design for Silicon Lifecycle Management

As reported recently by Dan Nenni, Siemens has signed an agreement to acquire Cambridge, UK-based UltraSoC Technologies Ltd. We’ve all seen plenty of mergers and acquisitions in EDA. Some transactions perform better than others. The best ones enhance an existing product or service by blending non-overlapping technologies.… Read More

The Future of Chip Design with the Cadence iSpatial Flow

A few months ago, I wrote about the announcement of a new digital full flow from Cadence. In that piece, I focused on the machine learning (ML) aspects of the new tool. I had covered a discussion with Cadence’s Paul Cunningham a week before that explored ML in Cadence products, so it was timely to dive into a real-world example of the … Read More

Fast and Accurate Variation-Aware Mixed-Signal Verification of Time-Domain 2-Step ADC

There is an interesting white paper out from Mentor on how a customer used the Solido Varation Designer tool to reduce Monte Carlo simulations. As you may know I worked for Solido for 10+ years up until they were acquired by Mentor in December of 2017. It was an incredible personal and professional experience. I have the highest respect… Read More

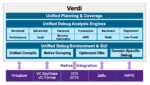

What’s New in Verdi? Faster Debug

Want fast debug? Synopsys recently hosted a Webinar to show off the latest and greatest improvements to Verdi® in performance, memory demand and multi-tasking, among other areas.

Performance improvements

Taruna Reddy (PMM) and Allen Hsieh (Staff apps) presented features of the latest version, released in March – Taruna started… Read More

Qualcomm on Power Estimation, Optimizing for Gaming on Mobile GPUs

I don’t look at the RTL power estimation topic too often these days, so I was interested to see that ANSYS still has a very strong position in this area. Qualcomm is using PowerArtist on one of the most demanding modern applications – mobile GPU power gaming. Mobile gaming heavily loads the GPU, so any optimization in that area will … Read More

Interview with Altair CTO Sam Mahalingam

In this interview we talk with Sam Mahalingam, chief technology officer at Altair, about gaining a competitive edge with software that’s built to handle high-throughput workloads like chip design and electronic design automation (EDA). Altair is a global technology company providing solutions in product development, high-performance… Read More

CEO Interview: John O’Donnel of yieldHUB

Let me introduce John O’Donnell, CEO of yieldHUB. After earning a degree in microelectronics John spent 18 years at Analog Devices before founding yieldHUB in 2005. If anybody knows yield it is Analog Devices having shipped billions upon billions of chips, absolutely.

SemiWiki will be digging deeper into the technology… Read More

Nobody Ever Lost Their Job for Spending too Much on Hardware Verification, Did They?

A paper was published last month on the Acuerdo Consultancy Services website authored by Joe Convey of Acuerdo and Bryan Dickman of Valytic Consulting. Joe and Bryan spent combined decades in the Semi and EDA World which means they have a great understanding of hardware bugs first hand, absolutely.

Here is a quick summary… Read More

Intel’s IDM 2.0