You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4169

[filter] => raw

[cat_ID] => 157

[category_count] => 4169

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

ClioSoft published a white paper recently entitled Best Practices are the Foundations of a Startup. The piece discusses the needs and challenges associated with building a scalable infrastructure to support growth.

Before I get into more details on ClioSoft’s white paper, I would offer my own experience on this topic – the need… Read More

Summary

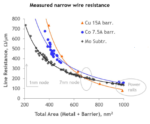

Design Technology Co-Optimization (DTCO) analysis was pursued for library cell PPA estimates for gate-all-around (GAA) devices and new metallurgy options. The cell design and process recommendations are a bit surprising.

Introduction

During the “golden years” of silicon technology evolution that applied Dennard… Read More

As most of you know DVCon 2020 was our first conference to be cut short by the Pandemic. SemiWiki bloggers Bernard Murphy, Mike Gianfagna, and I were there with full schedules but at the last minute it was called off. It really was an eerie feeling, the emptiness of it all.

The rest of our EDA live events followed suit and went virtual … Read More

As if engineers did not have enough difficulty just getting everything right so that their designs are implemented functionally correct, the demands of lowering power consumption require changes that can affect functionality and verification. Techniques such as power gating, clock gating, mixed supply voltage, voltage … Read More

Cadence vManager™ Verification Management provides what the company describes as metric-driven signoff. Anyone who has been through the tapeout process for a complex SoC knows the perils of verification sign-off. How much of the chip has been verified? What’s left to do? Will all be ready when the tapeout deadline arrives? … Read More

Rene Donkers, the company’s Co-founder and CEO, started his EDA career at Sagantec where he became responsible for world wide customer support and operations management. Ten years ago, Rene and a handful of people noticed a need in the design community for a standardized (portable) IP Validation approach to replace internal… Read More

I had the opportunity to preview an upcoming webinar from Synopsys on SoC Glitch Power – what it is and how to reduce it. There is some eye-opening information in this webinar. Glitch power is a bigger problem than you may think and Synopsys has some excellent strategies to help reduce the problem. The webinar is available via replay… Read More

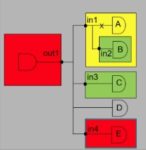

I love starting a new project from scratch, because there’s that optimistic feeling of having no constraints and being able to creatively express myself and get the job done right this time. For SoC designs today there are teams of engineers and maybe a program manager plus a marketing person that define the features, budget… Read More

Synopsys announced an addition to its popular DesignWare IP portfolio recently that has some significant ramifications. The company announced the industry’s first complete USB4 IP solution. Before we get into the details of the announcement, let’s take a quick look at the USB standard and why it’s important.

Standards… Read More

There is an old saying popularized by Mark Twain that goes “There are three kinds of lies: lies, damned lies, and statistics.” It turns out that no one can say who originated this saying, yet despite however you might feel about statistics, they play an important role in verifying analog designs. The truth is that there are large numbers… Read More

Intel’s IDM 2.0