There is an interesting white paper out from Mentor on how a customer used the Solido Varation Designer tool to reduce Monte Carlo simulations. As you may know I worked for Solido for 10+ years up until they were acquired by Mentor in December of 2017. It was an incredible personal and professional experience. I have the highest respect for the Solido Saskatoon development team which is why I wanted to do this white paper Q&A with Nebabie Kebebew, Sr. Product Manager, AMS Verification, Mentor, a Siemens Business.

Fast and Accurate Variation-Aware Mixed-Signal Verification of Time-Domain 2-Step ADC “To meet today’s analog-to-digital converter (ADC) specifications and to produce a high-yield design, teams typically need to perform extensive brute force mixed-signal simulations to account for all potential design variation. However, at nanometer nodes, the number of process, voltage and temperature (PVT) corners and parametric variation grow exponentially making the simulation impractical and costly. Teams attempt to employ extrapolation methods to shorten verification times. Learn how Analog Value Ltd. instead used Solido™ Variation Designer™ to perform PVT corner and Monte Carlo Simulation all at once to reduce simulations by orders of magnitude, but with the accuracy of brute force simulations.”

At advanced nodes meeting the ADC’s power, performance and area requirements are challenging. Why?

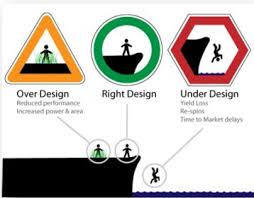

Advanced nodes present design challenges that include tighter timing margins and decreasing supply voltages, making variation effects worse. The number of process, voltage and temperature (PVT) corners grows significantly. This requires extensive SPICE simulations to account for all the potential design variations, making it costly and impractical. A fast and accurate variation-aware design and verification is necessary to meet the requirement for a high yield ADC design. In this case, a full-signoff level verification coverage across process, voltage, temperature (PVT) and Monte Carlo (MC) variation with a magnitude-of-order fewer simulation enables the designer to measure the influence of the analog block on the ADC performance. Another essential function is the ability to analyze and visualize the ADC’s sensitivity to variation, giving the designer insights on the possible trade-offs to improve the design yield.

Why is Mixed Signal simulation required for ADC design? Isn’t SPICE simulation sufficient?

To measure the performance of the ADC, one has to analyze its digital output. In general, for advanced ADC architectures, the digital output is generated by a sizable digital logic block that performs complex algorithms. And then there are analog blocks that require precise verification. Running SPICE on a large digital circuit together with the analog blocks slows down the simulation. There is also the requirement to analyze and verify the boundaries between the digital and analog circuits. Mixed-signal simulation is an essential element for fast and accurate verification of the ADC mixed-mode design.

Why is a “4-sigma” analysis of the comparator-latch block required to support a “3-sigma” analysis of the full time-domain ADC design?

In this case, the ADC IP is used in a large SOC, that has few to tens of these ADCs. With a 3-sigma design for the ADC, we are looking at ~ 1% expected yield loss. Typically, there are many comparator-latch blocks, in the range of 100s in each ADC. Achieving the 3-sigma target for the full ADC, requires a more stringent and higher sigma design for the sub-blocks. Hence, requiring the comparator-latch to be analyzed and verified to 4-sigma.

What is the user interaction required to add boundary elements in the analog-to-digital interfaces of the ADC for mixed-signal simulation?

The user interaction for adding a boundary element (BE) involves specifying or customizing parameters that control the boundary element behavior during simulation. Every design is unique. The different design specifications in terms of voltages levels, rise and fall times of the signals, output impedance seen by digital gates result in different requirements for the BE behavior. The requirements are realized through parameters on boundary element definitions that can be customized by the user for the specific target application. EDA tools typically provide a user interface and some level of automation to insert the BE and perform parameter customization.

What are the limitations of conventional statistical extrapolation method used by designers?

Due to limited computing resources and design schedule constraints designers are forced to run a limited number of brute force Monte Carlo simulation for the worst-case corners. Then they perform calculations to extrapolate to the target sigma. This approach is not optimal when working with a design complexity of an advanced node ADC with high yield requirement. It introduces a potential risk of missing the failures region and impacting the design yield.

For more product information you can check out the Solido Design Automation page on the Mentor website:

Variation-aware design & characterization

“With the acquisition of Solido Design Automation, Mentor becomes the leading provider of variation-aware design and characterization software, including Variation Designer and Characterization Suite product lines. Used by thousands of designers at most of the top 40 semiconductor companies worldwide. Solido provides the world’s most advanced variation-aware design and characterization software powered by proprietary machine learning technologies. The production-proven and versatile toolset is the easiest to use in its class and unparalleled in customer responsiveness.”

Comments

There are no comments yet.

You must register or log in to view/post comments.