Lurking inside of every Mosfet is a parasitic bipolar junction transistor (BJT). Of course, in normal circuit operation the BJT does not play a role in the device operation. Accordingly, SPICE models for Mosfets do not behave well when the BJT is triggered. However, these models work just fine for most purposes. The one important… Read More

Author: Tom Simon

Siemens Shows SOC Simulation Solution for Self-Driving Vehicles

Ever since the early days of computing there has always been a large distinction between ‘regular’ computing and real time computing – where special care had to be made to deal with unordered and asynchronous events. Back then a system typically consisted of a handful of sensors and perhaps some electromechanical devices.… Read More

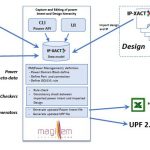

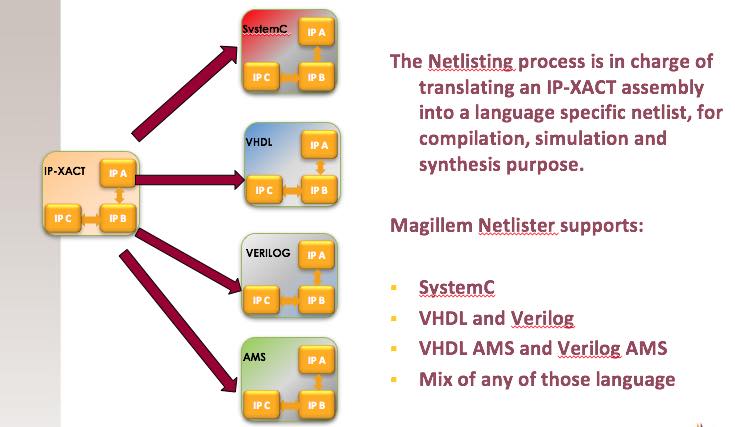

Magillem offers a practical UPF power flow

We already know that IP-Xact is extremely useful for managing IP and SOC design specifications, yet it may come as a surprise to learn that it also can be used to form the basis of a power flow too. There are design tools that read UPF to help implement and verify designs, however it can be extremely useful to understand the interplay … Read More

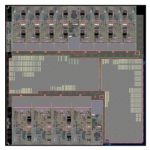

400G Ethernet test chip tapes-out at 7nm from eSilicon

Since the beginning of May eSilicon has announced the tape-out of three TSMC 7nm test chips. The first of these, a 7nm 400G Ethernet Gearbox/Retimer design, caught my eye and I followed up with Hugh Durdan, their vice president of strategy and products, to learn more about it. Rather than just respin their 56G SerDes, they decided… Read More

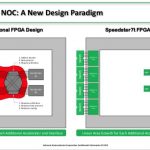

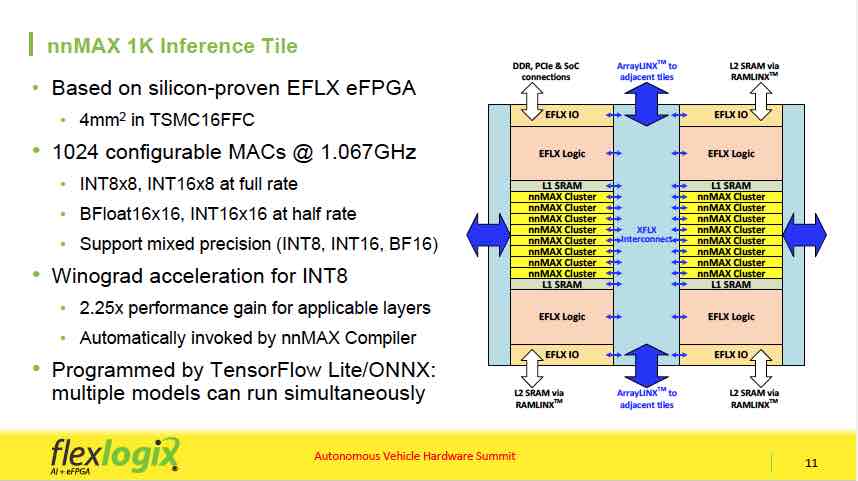

An evolution in FPGAs

Why does it seem like current FPGA devices work very much like the original telephone systems with exchanges where workers connected calls using cords and plugs? Achronix thinks it is now time to jettison Switch Blocks and adopt a new approach. Their motivation is to improve the suitability of FPGAs to machine learning applications,… Read More

The IoT will meet 5G soon, but not with the old SIM cards

By now you have probably realized that 5G is a lot more than an incremental change from previous 3G and 4G cellular technology. For instance, 5G will be used to connect our phones in completely new ways, such as with microcells in urban areas using mm-wavelength signals. 5G will also include two low power protocols that are intended… Read More

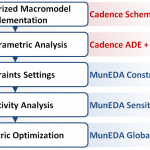

Free Webinar: Analog Verification with Monte Carlo, PVT Corners and Worst-Case Analysis

The letters “PVT” roll of the tongue easily enough, belying the complexity that variations in process, temperature and voltage can cause for analog designs. For semiconductor processes, there are dozens of parameters that can affect the viability of a design. It would be easy enough to optimize a circuit with only one or two varying… Read More

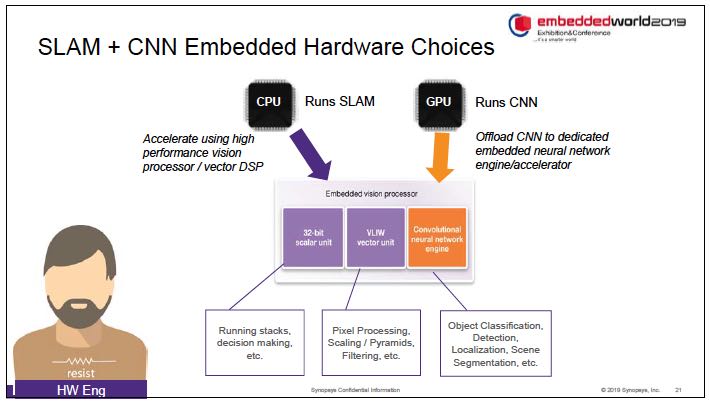

Using ML to Build Efficient Low Power Platforms for Augmented Vision

We are all pretty familiar with augmented reality, where real world images are overlaid with computer generated images, graphics and even audio. Of course, our first exposure to augmented reality might have been images of heads up displays in fighter jets or perhaps in the movie The Terminator. Augmented reality is moving rapidly… Read More

Real Time Object Recognition for Automotive Applications

The basic principles used for neural networks have been understood for decades, what have changed to make them so successful in recent years are increased processing power, storage and training data. Layered on top of this is continued improvement in algorithms, often enabled by dramatic hardware performance improvements.… Read More

IP-XACT The Answer for IP Reuse

To a lawyer, the term intellectual property means just about anything intangible that has value. However, when you bring that term up in the context of semiconductor design, it means something pretty specific to most people. Yet the implied meaning of the term intellectual property (IP) within the semiconductor field has changed… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center