It is pretty common for physical layout to work from a flattened hierarchy for blocks or even full chips, even though the front-end design starts with a hierarchical representation. This was not always the case. Way back when, the physical layout matched the logical hierarchy during the design process. Of course, this led to all… Read More

Author: Tom Simon

Adding CDM Protection to a Real World LNA Test Case

In RF designs Low Noise Amplifiers (LNA) play a critical role in system operation. They simultaneously need to be extremely sensitive and noise free, yet also must be able to withstand strong signal input without distortion. LNA designers often struggle to meet device performance specifications. Their task is further complicated… Read More

56th DAC – In Depth Look at Analog IP Migration from MunEDA

Every year at DAC, in addition to the hubbub of the exhibit floor and the relatively short technical sessions, there are a number of tutorials that dive in depth into interesting topics. At the 56th DAC in Las Vegas this year, MunEDA offered an interesting tutorial on Analog IP migration and optimization. This is a key issue for large… Read More

Virtuoso Adapts to Address Cyber Physical Systems

LIDAR is a controversial topic, with even Elon Musk weighing in on whether it will ever be feasible for use in self driving cars. His contention is that the sensors will remain too expensive and potentially be unreliable because of their mechanical complexity. However, each of the sensors available for autonomous driving have … Read More

Synopsys and Synaptics Talk About Securing the Connected Home

Like many people, I have been adding automation to my home, and the number of connected devices I use has slowly but steadily increased. These include light bulbs, cameras, switches, a thermostat, a voice assistant, etc. Between them, they know when I am home or away, and have the ability to record images and sound. In addition to … Read More

HBM or CDM ESD Verification – You Need Both

In the realm of ESD protection, Charged Device Model (CDM) is becoming the biggest challenge. Of course, Human Body Model (HBM) is still essential, and needs to be used when verifying chips. However, a number of factors are raising the potential losses that CDM events can cause relative to HBM. These factors fall into two categories:… Read More

Automotive Market Pushing Test Tool Capabilities

It’s easy to imagine that the main impetus for automotive electronics safety standards like ISO 26262 is the emergence of autonomous driving technology. However, even cars that do not offer this capability rely heavily on electronics for many critical systems. These include engine control, braking, crash sensors, and stability… Read More

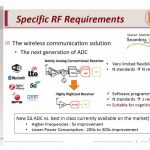

Dynamic Spectrum Allocation to Help Crowded IoT Airwaves

Radio frequency bandwidth has become a precious commodity, with communications companies paying top dollar for prized pieces of the spectrum. However, many radio bands are not often used efficiently. Many existing radio protocols exchange data on a fixed pair of frequencies, tying up those frequencies for other users. When… Read More

Upcoming HBM and CDM ESD Verification Seminar in Taiwan

The electrostatic discharge that occurs in lightening, as seen in the picture below, can cause serious damage to the objects on the ground. Over centuries mankind has devised ways, such as lighting rods and arresters, to deflect the energy so it is dissipated harmlessly. The same drama plays out on modern semiconductors due to … Read More

#56thDAC Discussion on Calibre in the Cloud Brings Sunshine to SOC Developers

It was inevitable that EDA applications would meet the cloud. EDA has a long history of creating some of the most daunting compute challenges. This arises from employing current generation chips to design the next generation chips. Despite growing design complexity, many tools have kept pace and even reduced runtimes from generation… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center