Is that an IoT patent application I see pinned to your desktop? A new analysis by technology intellectual property legal experts LexInnova confirms IoT patents are being generated rapidly – and looks at which classes of patents are likely to be worth something in acquisition or litigation.… Read More

Author: Don Dingee

Moving chips from industrial to industrial IoT

IHS has put out its 1Q2016 Application Market Forecast predicting the highest growth rate segments for semiconductors over the next five years – and what was once old is new yet again. There it is, in the top right corner: industrial, projected to outpace even the automotive sector.… Read More

ARM tests out TSMC 10FinFET – with two cores

About 13 months ago, the leak blogs posted news of “Artemis” on an alleged ARM roadmap slide, supposedly a new 16FF ARM core positioned as the presumptive successor to the Cortex-A57. Now, we’re finding out what “Artemis” may actually be, inside a multi-core PPA test chip on TSMC 10FinFET.… Read More

Testing IGBTs before they go into EVs

In the pages of SemiWiki, we are usually talking about what to do with billions of really small transistors – for a change of pace today, we’ll discuss what to do with a few really big ones. Mentor Graphics has just announced their latest MicReD platform for thermal testing of IGBTs, experiencing a resurgence (pun intended) thanks… Read More

Aldec extends FPGA and ASIC flows at DAC

Aldec tools and services have long been associated with FPGA designs. As FPGAs have evolved toward more RTL-based designs, the similarities between a modern FPGA verification flow and an ASIC verification flow often leave them looking virtually the same. … Read More

S2C tutorial and PROTOTYPICAL debut at DAC

It’s been a busy few days here in Canyon Lake, and we’re ready to share exciting news in advance of #53DAC coming up on Monday, June 6[SUP]th[/SUP]. S2C is offering a technical program tutorial on “Overcoming the Challenges of FPGA Prototyping” followed by the launch of our latest book project, “PROTOTYPICAL”, including a field… Read More

Sonics opens new strategy for SoC energy processing

Back in February when we shared the Sonics philosophy on the ICE-Grain Power Architecture for hardware-based SoC power management, I speculated we’d know more by DAC 2016. Sonics is hitting the road with a new live seminar coming to Silicon Valley this month and Austin during DAC – and the news is big.… Read More

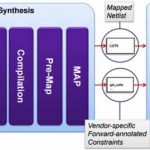

One FPGA synthesis flow for different IP types

Both Altera and Xilinx are innovative companies with robust ecosystems, right? It would be a terrible shame if you located the perfect FPGA IP block for a design, but couldn’t use it because it was in the “wrong” format for your preferred FPGA. What if there were a way around that?

There is a compelling argument to use each FPGA vendor’s… Read More

Body-biasing for ARM big or LITTLE in GF 22FDX

GLOBALFOUNDRIES has been evangelizing their 22FDX FD-SOI process for a few months; readers may have seen Tom Simon’s write-up of their preview at ARM TechCon. Dr. Joerg Winkler recently gave an updated webinar presentation of their approach in an implementation of ARM Cortex-A17 core.

By now, you’ve probably heard that 22FDX… Read More

BLDC motor control kit targets power savings

We tend to focus on connectivity and sensors for the IoT, however there is a third element to what I call the “Edge Device Triad” that is just as important: actuators. Making things move with microcontrollers (MCUs) is a science in and of itself. For small size and low weight combined with decent mechanical power, designers are opting… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era