One of the things that I miss most about attending trade shows like DAC in the old days was that you actually got to see EDA tools being demonstrated live in the exhibit area. You could see what the GUI looked like, how the dialogs worked, and learn what kind of control you could have during analysis. Most of what you see today at DAC in the… Read More

Author: Daniel Payne

Drift is a Bad Thing for SPICE Circuit Simulators

My first job out of college was with Intel, located in Aloha, Oregon and I did circuit simulations using a proprietary SPICE circuit simulator called ASPEC that was maintained in-house. While doing some circuit simulations one day I noticed that an internal node in one of my circuits was gradually getting higher and higher, even… Read More

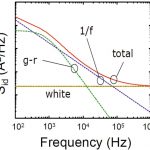

Why is Low Frequency Noise Measurement for ICs Such a Big Deal?

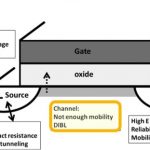

Even digital designers need to be aware of how noise impacts their circuits because most clocked designs today use a Phase Locked Loop (PLL) block which contains a circuit called a Voltage Controlled Oscillator (VCO) that is quite sensitive in operation to the effects of noise and process variation. As process node scaling continues… Read More

RTL Design Restructuring Explained

Modern SoC designs can use billions of transistors where transistors are grouped into gates, then gates grouped into cells, then cells grouped into blocks, blocks grouped into modules, and so on, creating a complex hierarchy. What a front-end designer conceives of logically for a hierarchy will differ from how an optimized physical… Read More

Requirements Management and IP Management Working Together

I first heard about requirements management back in 1995 while marketing a graphic HDL entry tool for an EDA vendor, and it sounded like a very useful automation approach, however our team quickly discovered that there were too many different vendors for requirements management, so there could be no simple way to integrate with… Read More

Power-Aware Debug to Find Low-Power Simulation Bugs

When I worked at Intel designing custom chips my management would often ask me, “Will first silicon work?” My typical response was, “Yes, but only for the functions that we could afford to simulate before tape-out.” This snarky response would always cause a look of alarm, quickly followed by a second … Read More

Five Things To See at DVCon India 2016

DVCon is an annual Design and Verification Conference that started out in Silicon Valley, then expanded by adding India as a new location. Our semiconductor design and verification world is global in stature, so if you’re living in the region then consider registering for this event held Thursday and Friday, September … Read More

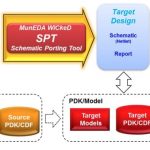

Three Steps for Custom IC Design Migration and Optimization

Popular companies designing smart phones, CPUs, GPUs and Memory components all employ teams of custom IC designers to create the highest performance chips that are as small as possible, and at the lowest costs. How do they go about doing custom IC design migration and optimization when moving from one process node to another one?… Read More

Low Frequency Noise Challenges IC Designs

AMS and RF IC designers have known for years that their circuits are sensitive to noise, because if you amplify noise on an input source to an amplifier circuit then your chip can start to produce wrong answers. Even digital SoC designers need to start taking notice because every SoC is filled with SRAM IP blocks, and at each shrinking… Read More

Did My FPGA Just Fail?

Designing DRAMs at Intel back in the 1970s I first learned about Soft Errors and the curious effect of higher failure rates of DRAM chips in Denver, Colorado with a higher altitude than Aloha, OR. With the rapid growth of FPGA-based designs in 2016, we are still asking the same questions about the reliability of our chips used for safety-critical… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?