How much perfectly good silicon is being discarded in the quest for reliability? During high-volume chip manufacturing, aggressive testing with strict thresholds may ensure quality but reduces yield, discarding marginal chips that could function flawlessly. On the other hand, prioritizing yield risks allowing defective chips into the field, leading to costly return merchandise authorizations (RMAs), system failures, or Silent Data Corruption (SDC). SDC, in particular, is a stealthy threat that causes undetected faults to propagate through the system, leading to catastrophic outcomes. So how do you strike the balance between rigorous error detection while maintaining yield?

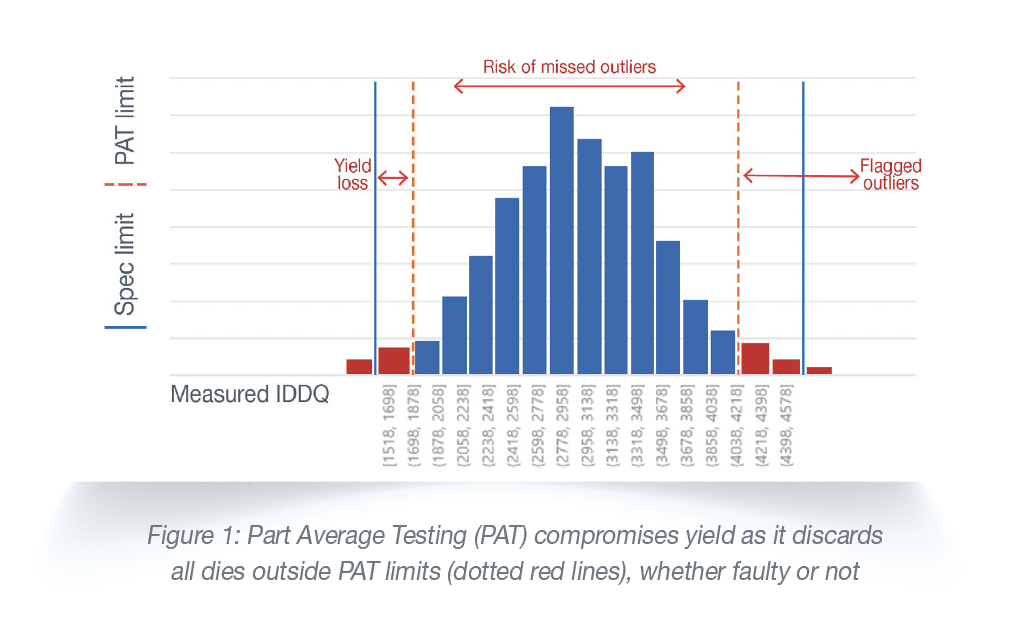

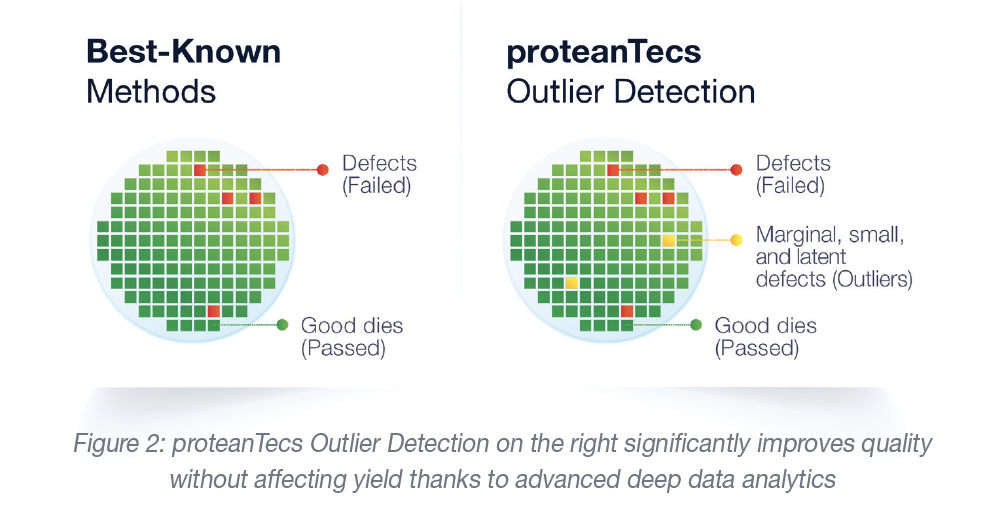

Conventional methods like Part Average Testing (PAT) or Good Die in a Bad Neighborhood (GDBN) rely on statistical analysis to improve quality but are limited in granularity. They miss subtle defects while discarding healthy chips, exacerbating the quality-yield tradeoff. Thus, chipmakers have historically faced the tricky challenge of improving quality while preserving yield. Striking this balance is essential for industries like automotive and data centers, where reliability and performance are critical.

Chipmakers can now overcome this tricky challenge using proteanTecs’ outlier detection solution. proteanTecs recently published a whitepaper that discusses the details of this solution.

proteanTecs Solution: A Paradigm Shift in Outlier Detection

proteanTecs Outlier Detection redefines semiconductor testing by integrating telemetry-based data analytics and machine learning (ML) to detect latent defects early, even at the wafer sort stage. Embedded Agents in chips collect parametric data, which proteanTecs analyzes using advanced algorithms. These models predict normal chip behavior and identify anomalies that traditional pass/fail tests cannot detect.

proteanTecs’ solution includes edge software deployed on testers and a cloud-based analytics platform. The edge software compares predicted behavior with real-time test data, flagging outliers for further review or discard before chips progress down the production line. Additionally, the software provides resiliency to prevent production drift using both local and distribution-based drift detection mechanisms.”

IDDQ Prediction-Based Detection

This method identifies leakage current anomalies at the transistor level, targeting defects invisible to traditional tests. proteanTecs combines design-profiling and process-classification data to train predictive ML models that estimate the expected IDDQ per chip. By comparing measured and predicted values during testing, latent defects are flagged and discarded. This approach not only prevents field failures but also reduces false positives that could unnecessarily lower yield.

Timing Margin-Based Detection

This method monitors timing issues at both the transistor and path levels. proteanTecs’ Margin Agents monitor timing margins across millions of IC logical paths, identifying subtle timing issues below conventional pass/fail thresholds. ML models trained on expected timing behavior detect deviations that signal potential field failures, such as timing faults or SDCs. Unlike tightening traditional test limits, this approach detects marginal defects without compromising yield.

How proteanTecs’ Outlier Detection Stands Apart

Traditional Best-Known Methods (BKMs) rely on statistical population analysis and stricter thresholds, leading to blind yield losses and missed defects. proteanTecs surpasses these limitations by leveraging dedicated on-chip Agents and predictive analytics. Its solutions operate beyond pass/fail metrics, detecting anomalies with unmatched granularity and precision. By integrating machine learning with hardware telemetry, proteanTecs enables manufacturers to meet stringent quality standards without compromising yield, delivering a dual benefit previously considered unattainable.

Benefits of proteanTecs’ Solution

proteanTecs enhances quality assurance by isolating chips with latent defects, ensuring higher reliability and performance while minimizing the risk of defective chips reaching consumers. By distinguishing true defects from benign variances, it improves yield, enabling the recovery of chips that would otherwise be discarded. This reduces waste and boosts productivity. Early detection of latent defects also prevents costly returns (RMAs) and silent data corruption (SDC), ensuring system reliability throughout the product lifecycle. Addressing issues at the Wafer Sort stage saves time and resources, reducing downstream testing, rework and packaging costs.

proteanTecs’ cloud-based platform aggregates data from chips, wafers, and lots, enabling comprehensive analysis across test stages. With advanced visualization tools, historical data storage, and real-time insights, it supports root cause analysis and proactive decision-making. Additionally, proteanTecs’ machine learning algorithms continuously refine their models, adapting to evolving manufacturing processes and ensuring ongoing detection accuracy in dynamic environments.

Tangible Proof Points from Customers

Automotive: Over time, automotive electronic systems have become the most complex element of vehicle architecture. Software in today’s cars can contain more than 100 million lines of code. Reliable implementation of these advanced technologies must meet stringent zero-downtime requirements, while accommodating unpredictable environmental and operational conditions. One manufacturer reduced Defective Parts Per Million (DPPM) by 396 using proteanTecs’ IDDQ-based detection, saving over $250,000 in testing and packaging costs. HTOL testing validated the effectiveness, with 70% of flagged outliers failing stress tests. Read case study here: Automotive Chipmaker Slashes DPPM With ML-Powered Outlier Detection.

Data Centers: As datacenters scale to accommodate the requirements for AI applications, the demand for reliable and high-performance semiconductors increases. Semiconductor reliability is essential to maintain the uninterrupted performance of critical systems that require continuous and real-time operation. A networking chipmaker decreased DPPM by 252, avoiding latent defects that could snowball into RMAs. This early detection saved over $1,000,000 by eliminating late-stage failures and system disruptions. Read more here in our white paper: Redefining RAS in Datacenters with Real-Time Health Monitoring White Paper

Real-Time Analytics for Reliability and Cost Efficiency

proteanTecs represents a new era in semiconductor testing, combining real-time analytics, adaptive learning, and actionable insights. Its transformative approach is imperative for industries where reliability and performance cannot be traded off. By addressing the root causes of chip failures and slashing DPPM rates, proteanTecs empowers manufacturers to exceed customer expectations while reducing operational costs.

For chipmakers navigating stringent quality and yield demands, proteanTecs’ outlier detection solution is a necessity for staying competitive in a precision-driven market.

Access the whitepaper from here: “Cut Defects, Not Yield: Outlier Detection with ML Precision”

Also Read:

2025 Outlook with Uzi Baruch of proteanTecs

Datacenter Chipmaker Achieves Power Reduction With proteanTecs AVS Pro

Podcast EP214: The Broad Impact of proteanTecs with Noam Brousard

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.