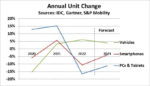

Automotive appears to be about the only bright spot in the semiconductor market for 2023. Forecasts for the overall semiconductor market range from a decline of 4% to a decline of 20%. Semiconductor companies generally have bleak outlooks for the start of 2023, citing excess inventories ad weak end market demand. The chart below shows annual unit change for the key semiconductor market drivers PCs & tablets, smartphones, and motor vehicles. PCs and tablets boomed in the first two years of the COVID-19 pandemic but declined 17% in 2022. IDC projects an 11% decline in PCs & tablets in 2023. Smartphones dropped 11% in 2022 after 6% growth in 2021. Gartner expects smartphone units to drop 4% in 2023. Light vehicle production declined 15% in 2000 after automakers cut back production over concerns related to the pandemic. Light vehicles returned to growth in 2021 at 3% and in 2022 at 6%. S&P Global Mobility is forecasting a 4% increase in light vehicles produced in 2023.

Automotive Semiconductor Companies

The top five semiconductor suppliers to the automotive industry are shown in the chart below. Infineon is the largest at $8.1 billion in automotive semiconductor revenue in 2022. The top five account for about half of the total automotive semiconductor market. These companies experienced strong growth in the automotive market in 2022, ranging from 17% to 46%, compared to only 3.3% growth in the overall semiconductor market. Automotive is a significant portion of these companies’ overall revenues, ranging from 25% to 52%.

The top five companies have all provided revenue guidance for 1Q 2023 calling for a decline in total revenue from 4Q 2022 (except for Renesas, which did not provide guidance). However, each company cited the automotive segment as remaining strong. In its 4Q 2022 earnings conference call, NXP cited a “pricing tailwind” for automotive, implying increasing prices.

Automotive Semiconductor Market

The automotive semiconductor market should show healthy growth in 2023, in contrast to most of the rest of the semiconductor market. We at Semiconductor Intelligence are forecasting 14% growth for the automotive semiconductor market in 2023. Key factors driving this growth are:

· Strong revenue momentum for semiconductor suppliers

· Easing of semiconductor shortages, but some remaining through 2023

· Automotive semiconductor inventories generally below desired levels

· Some price increases for automotive semiconductors

· Growth of 4% or more in vehicle production

· Continued increases in semiconductor content per vehicle

The longer-term outlook for automotive semiconductors is also very healthy. The semiconductor content per vehicle will steadily increase over the next several years. S&P AutoTechInsight in January 2023 projected the average semiconductor content per vehicle will increase 80% over the next seven years from $854 in 2022 to $1,542 in 2029.

A McKinsey & Company report from April 2022 projected the overall semiconductor market will pass a trillion dollars at $1,065 billion in 2030, a compound annual growth rate (CAGR) of 6.8% from 2021. The automotive semiconductor market is expected to reach $150 billion in 2030, a CAGR of 13.0% from 2021. Thus, the automotive semiconductor CAGR is almost twice the growth rate of the overall semiconductor market.

The key drivers of automotive semiconductors through the end of the decade are electric vehicles (EVs), driver-assistance systems and autonomous-driving, and infotainment systems.

Electric Vehicles – Battery Electric Vehicle (BEV) sales were about 10 million units in 2022, about 12% of total vehicles sold, according to Counterpoint Research. Counterpoint estimates about 40% of vehicles sold in 2030 will be BEV. Several major automakers including Honda, Volkswagen and Hyundai are targeting BEVs to account for 50% or more of production by 2030. BEVs require sophisticated battery management systems. BEVs are estimated to have semiconductor dollar content two times (according to X-FAB) to three times (according to Analog Devices) the content of internal combustion engine vehicles. Thus, the shift to high semiconductor value BEVs will significantly contribute to the overall growth of automotive semiconductors.

Driver assistance and autonomous-driving – vehicles are increasingly incorporating technology to aid the driver such as adaptive cruise control, lane keeping assistance, rearview video, and automatic emergency braking. These features require numerous sensors and controllers. According to the Statista Mobility Market Insights, cars with at least some driver assistance features accounted for 86% of sales in 2020 compared to just 49% in 2015. McKinsey & Company estimates the 2022-2030 CAGR of driver assistance systems at 17%

Fully self-driving cars or autonomous vehicles (AV) will be slower to develop. McKinsey projects only 12% of cars sold in 2030 will be AVs, increasing to 37% in 2035. Adoption of AVs will require advances in technology, changing consumer attitudes and changing government regulations. Tesla reported its vehicles using Autopilot technology in the U.S. averaged over 5.6 million miles per accident in 2022 compared to 652 thousand miles per accident for the U.S. overall. Although the Autopilot accident rate is about one-ninth of the overall rate, one could argue AVs should be orders of magnitude safer than human drivers. A 2023 AAA survey showed 68% of U.S. drivers are afraid of self-driving vehicles, with 23% unsure and only 9% trusting them.

Infotainment – a combination of information and entertainment these systems provide services such as navigation systems, wi-fi, smartphone integration, voice commands, audio, and video. The vast majority of cars sold today include infotainment systems, especially in advanced nations. Analysts estimate the CAGR of the automotive infotainment market from 2022 to 2030 at about 9% to 11%.

The automotive semiconductor industry looks strong in 2023 and through the end of the decade. The increasing semiconductor content of vehicles will make automotive the fastest growing major segment of the semiconductor market through 2030.

Semiconductor Intelligence is a consulting firm providing market analysis, market insights and company analysis for anyone involved in the semiconductor industry – manufacturers, designers, foundries, suppliers, users or investors. Please contact me if you would like further information.

Bill Jewell

Semiconductor Intelligence, LLC

billjewell@sc-iq.com

Also Read:

CES is Back, but is the Market?