Two important trends will be discussed in this book: The disruptive nature of the Internet of Things and the use of the ASIC business model by systems companies to get into the chip business.… Read More

Tag: synopsys

Enabling a New Semiconductor Revolution!

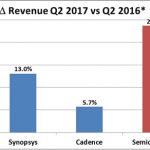

According to semiconductor trade statistics, 2017 will be the strongest market since 2010 easily recording double digit gains causing the SOX Semiconductor Index to outpace NASDAQ and the other indexes. The question Wall Street people have now is: How much longer will semiconductors be an attractive investment? That question… Read More

Semiconductor and EDA 2017 Update!

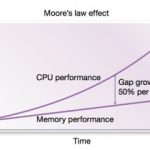

It really is an exciting time in semiconductors. The benchmarks on the new Apple A11 SoC and the Nvidia GPU are simply amazing. Even though Moore’s Law is slowing, the resulting chips are improving well above and beyond expectations, absolutely.

As I have mentioned before, non-traditional chip companies such as Apple, Amazon,… Read More

ATopTech is Back!

One of the biggest surprises at the TSMC OIP Forum last week was the reappearance of bankrupt EDA vendor ATopTech. I spoke with former ATopTech CEO and now Avatar IS President Jue-Hsien Chern at OIP. As a survivor of several EDA legal battles myself, I understand what ATopTech went through and I am thoroughly impressed that they had… Read More

Breakfast with Aart de Geus and the Foundries!

Being the number one EDA and the number one IP company does have its advantages and the resulting foundry relationships are a clear example. One of the DAC traditions that I truly enjoy is the Synopsys foundry breakfasts. Not only does Synopsys welcome scribes, they reserve a table up front for us and Synopsys CEO Aart de Geus has been… Read More

Samsung, Synopsys and Qualcomm at DAC

I’m a user of many Samsung products as my family has Samsung Galaxy smart phones and my MacBook Pro uses Samsung SSD for storage, so at DAC I attended a breakfast panel with presenters from Samsung, Synopsys and Qualcomm. This was the second day of DAC and they served us breakfast, and with the big names on the panel the room was… Read More

TSMC OIP Ecosystem Forum 2017 Preview!

The TSMC OIP Ecosystem Forum is upon us again. I have yet to meet a disappointed attendee so it is definitely worth your time: Networking with more than 1,000 semiconductor professionals, the food, mingling with the 50+ EDA, IP, and Services Companies, the food, and of course the content. The 7nm and 7nm EUV updates alone are worth… Read More

HBM offers SOC’s dense and fast memory options

Dual in-line memory modules (DIMM’s ) with double data rate synchronous dynamic random access memory (DDR SDRAM) have been around since before we were worried about Y2K. Over the intervening years this format for provisioning memory has evolved from supporting DDR around 1995, to DDR1 in 2000, DDR2 in 2003, DDR4 in 2007 and DDR4… Read More

HLS update from Mentor about Catapult

I recall back in the late 1980’s when logic synthesis tools were first commercialized, at first they could read in a gate-level netlist from one foundry then output an optimized netlist back into the same foundry. Next, they could migrate your gate-level netlist from Vendor A over to Vendor B, giving design companies some… Read More

LETI Days 2017: FD-SOI, Sensors and Power to Sustain Auto and IoT

I have attended last week to the LETI Days in Grenoble, lasting two days to mark the 50[SUP]th[/SUP] anniversary of the CEA subsidiary. Attending to the LETI Days is always a rich experience: LETI is a research center counting about 3000 research engineers, but LETI is also a start-up nursery. The presentations are ranging from … Read More