If Cadence is making money with large VIP port-folio, Synopsys has successfully deployed an acquisition strategy to build a large Design IP port-folio. Looking at these acquisitions will help understanding Synopsys positioning in the IP market. When they have started this acquisition campaign, back in 2002, their market share… Read More

Tag: synopsys

Synopsys MIPI Webinar

Synopsys MIPI Webinar: MIPI is really getting traction

Synopsys last two acquisitions of IP vendors, former ChipIdea in 2009 (Mixed-signal product line of MIPS) and Virage Logic in 2010, have allowed to built a stronger, diversified IP port-folio. Amazingly, Synopsys has found MIPI IP product line in the basket in both cases.… Read More

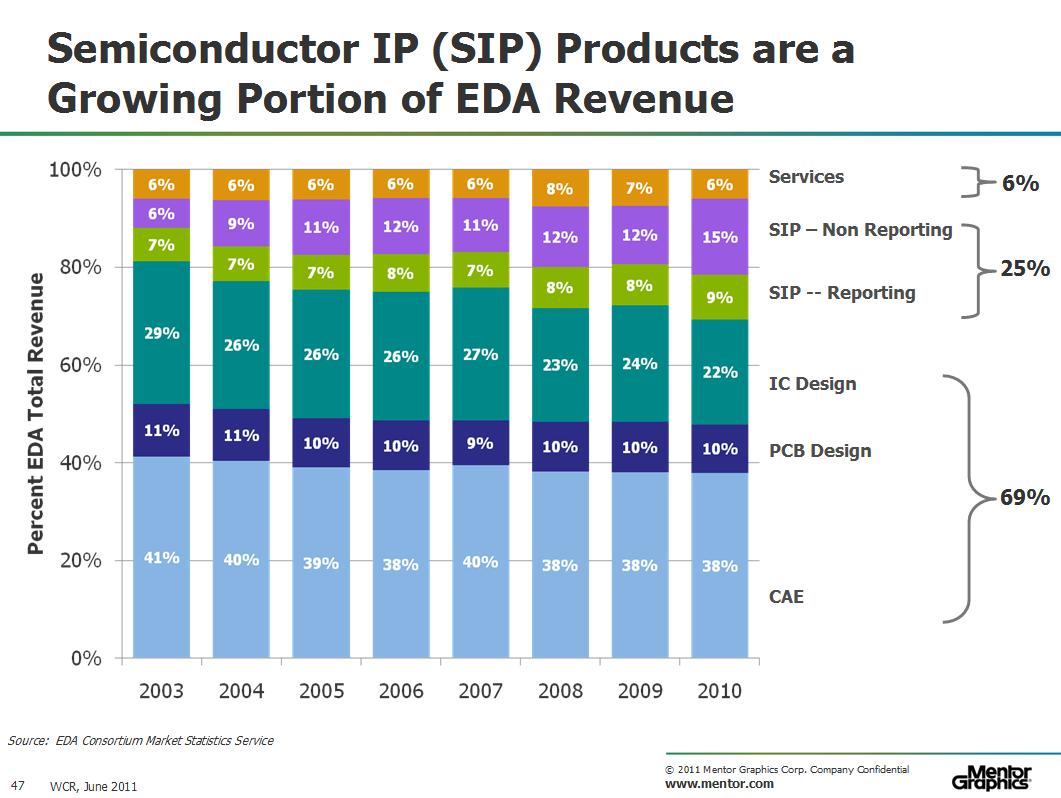

Silicon IP to take over CAE in EDAC results… soon but not yet!

Very interesting results launched by EDAC for Q1 2011, if Computer Aided Engineering (CAE) is still the largest category with $530.6M, the second category is Silicon IP (SIP) with $371.4M, followed by IC Physical Design & Verification at $318.5M. Even more significant is the four quarter moving average results, showing … Read More

Semiconductor IP State of the Union

After the mega IP acquisitions last year by Cadence (Denali) and Synopsys (Virage) a lot of people are wondering what is next for the commercial Semiconductor IP market. Let me offer my opinion as a person who works closely with foundries and their top customers and the opinion of Dr. Eric Esteve, an expert on interface IP.

The commercial… Read More

Synopsys IC Validator at DAC

Intro

At DAC last week I visited the Synopsys demo suite to see what’s new with IC Validator.

Notes

Stelios Diamantidis, PMM

– In-design physical verification

– Sign-off reveals thousands of late stage DRC violations

– 28nm has 1.5K rules, 15K runset sizes

– Metal Fill changes timing

– The… Read More

Synopsys, ARM, Samsung, GLOBALFOUNDRIES (Part 1 of 2)

Intro

The 28nm nodes is ready with foundry silicon, IP and EDA tools. Tuesday morning at the DAC breakfast I learned more about the 28nm eco-system.

Notes

Why 32/28nm

–Lower power, high integration requirements, mobile applications

What is Ready?

–IP is qualified (ARM, Memories, Foundation IP, SNPS IP, PDKs)

–… Read More

HSPICE gets Faster, better Convergence

Hany El Hak – Product Marketing Manager

Frederik Iverson – AE

Scott Wetch – HSPICE Architect

HSPICE – 5 years ago convergence was not so good, while 95% of analog circuits today converge out of the box, no options are required.

Synopsys AMS Portfolio – wide range of tools

– Custom Designer: IC schematic and layout tools

–… Read More

iPDKs and Analog Constraints

Lunch time Monday at DAC and I learned about what’s new at the IPL Alliance in 2011.

IPL Sponsors: Magma, Mentor Graphics, Springsoft, Accelicon, Ciranova, Synopsys, TSMC, TowerJazz, Jedat, Tanner EDA

Two major projects:

1) iPDKS

2) Analog Constraints… Read More

Mentor 2 : Carl Icahn 0

The corporate raiders are still throwing rocks at Mentor Graphics. I have followed this reality show VERY closely and find their latest assault seriously counterproductive. Disinformation is common in EDA but I expected more from Carl Icahn and the Raiderettes. They are quite the drama queens. Here is a billion dollar question:… Read More

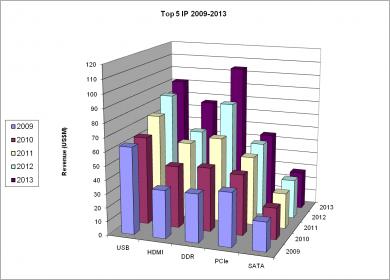

DDR4 Controller IP, Cadence IP strategy… and Synopsys

I will share with you some strategic information released by Cadence last week about their IP strategy, more specifically about the launch of the DDR4 Controller IP. And try to understand Cadence strategy about Interface IP in general (USB, PCIe, SATA, DDRn, HDMI, MIPI…) and how Cadence is positioned in respect with their closest… Read More