You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Introduction from Hezi Saar: Eric’s latest viewpoints and reports are host onIPnestas well as on Semiwikiand you can find information related to various Interface IP: USB 3.0, PCIe, SATA, DDRn, MIPI, HDMI and more.

Q: Eric, give us a quick introduction about your background as it relates to interface IP

A: I have spent 20 years working… Read More

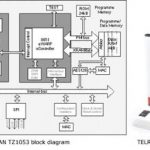

Very interesting question from Zahrein in this thread: “how to manage an embedded USB 3.0 PHY Verification”? To clearly position the problem, Zahrein need to run the RTL verification of a complete SoC integrating an USB 3.0 function, that is the Controller (digital) and the PHY (Analog Mixed Signal) embedded in the SoC. The question,… Read More

Intro

My first exposure to hardware prototyping was at Intel back in 1980 when the iAPX 432 chip-set group decided to build a TTL-based wire-wrap prototype of a 32 bit processor to execute the Ada language. The effort to create the prototype took much longer than expected and was only functional a few months before silicon came back.… Read More

I read about how Toumaz used the Analog Fast SPICE (AFS) tool from BDA and it sounded interesting so I setup a Skype call with Alan Wong in the UK last month to find out how they design their ultra low-power IC chips.

Interview

Q: Tell me about your IC design background.

A: I’ve been at Toumaz almost 8 years now and before that at Sony… Read More

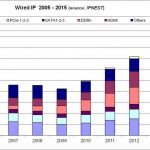

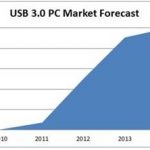

SuperSpeed USB specification was released in November 2008! Even if we can see USB 3.0 powered peripherals shipping now, essentially external HDD, connected to PC equipped with Host Bus Adaptors (as PC chipset from Intel or AMD were not supporting USB 3.0), it will take up to the second quarter of 2012 before PC will be shipped with… Read More

Way back in 1999 the open SystemC initiative (OSCI) was launched. In 2005 the IEEE standard for SystemC (IEEE1666-2005 if you are counting) was approved. In 2008, TLM 2.0 was standardized (transactional level models), making building virtual platforms using SystemC models easier. At least the models should be play nicely together,… Read More

The acquisitions of Virage Logic by Synopsys in 2010, have allowed building a stronger, diversified IP port-folio, including the embedded SRAM, embedded non-volatile memory and embedded test and repair solution. Looking back in time, I remember the end of the 80’s: at that time the up-to-date solution to embed SRAM in your ASIC… Read More

There are various rumors around about Cadence starting to close up stuff that has been open for a long time. Way back in the midst of time, as part of the acquisition of CCT, the Federal Trade Commission forced Cadence to open up LEF/DEF and allow interoperability of Cadence tools (actually only place and route) I believe for 10 years.… Read More

Even if nSys acquisition by Synopsys will not have a major impact on Synopsys’ balance sheet, it is a kind of earthquake in the Verification market landscape. After the Denali acquisition by Cadence in 2010, nSys was most probably the market leader in verification IP, if we look at the independent VIP providers (excluding Cadence).… Read More

The CEO panel at the 2nd GTC wasn’t especially enlightening. The theme was that going forward will require cooperation for success and everyone was really ready to cooperate.

The most interesting concept was Aart talking about moving from what he called “scale complexity” aka Moore’s law to what he … Read More