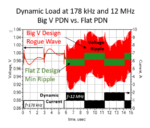

Advanced board designs are fertile ground for misbehavior in time and frequency domains. Relying on intuition, then waiting until near-final product for power integrity (PI) or EMI testing almost guarantees board respins are coming. Lumped-parameter simulations of on-board power delivery networks (PDNs) struggle with … Read More

Tag: simulation

Fully Modeling the Semiconductor Manufacturing Process

A lot of folks in the semiconductor business are familiar with Dassault Systèmes because of their product life cycle management (PLM) products for IC design. They are, of course well known in other industries as well for their 3D modeling and simulation software. Over the years they have added capabilities and intelligence to … Read More

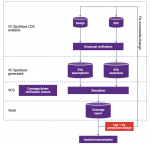

Techniques and Tools for Accelerating Low Power Design Simulations

I recently watched a webinar titled “How to accelerate power-aware simulation debug with Synopsys’ VC LP” that was presented by Ashwani Kumar Dwivedi senior applications engineer at Synopsys. Watching the webinar made me reminisce how design verification has evolved over the years. A long time ago, static verification started… Read More

Siemens PAVE360 Stepping Up to Digital Twins

The idea of a digital twin is simple enough. You use a digital model of a car, aircraft, whatever to test design ideas and prove your design will be robust across a wide range of scenarios before you commit millions of dollars and lives to proving out the real thing. As Siemens have accomplished in their PAVE360 platform. There are a … Read More

Webinar Replay – Insight into Creating a Common Testbench

These days the verification process starts right when the design process begins, and it keeps going well past the end of the design phase. Simulation is used extensively at every stage of design and can go a long way to help validate a design. However, for many types of designs, especially those that process complex data streams, … Read More

What’s New in CDC Analysis?

Synopsys just released a white paper, a backgrounder on CDC. You’ve read enough of what I’ve written on this topic that I don’t need to re-tread that path. However, this is tech so there’s always something new to talk about. This time I’ll cover a Synopsys survey update on numbers of clock domains in designs, also an update on ways to… Read More

Solving and Simulating in the New Virtuoso RF Solution

Cadence has done a good job of keeping up with the needs of analog RF designs. Of course, the term RF used to be reserved for a thin slice of designs that were used specifically in RF applications. Now, it covers things like SerDes for networking chips that have to operate in the gigahertz range. Add that to the trend of combining RF and… Read More

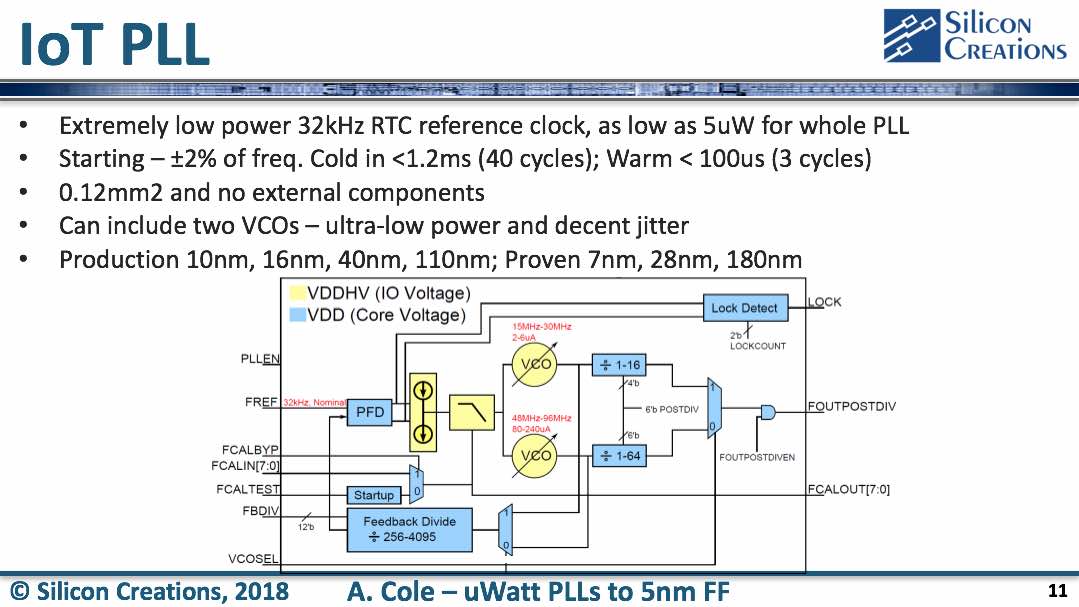

Essential Analog IP for 7nm and 5nm at TSMC OIP

When TSMC’s annual Open Innovation Platform Exposition takes place, you know it will be time to hear about designs starting on the most advanced nodes. This year we were hearing about 7nm and 5nm. These newer nodes present even more challenges than previous nodes due to many factors. Regardless of what kind of design you are undertaking… Read More

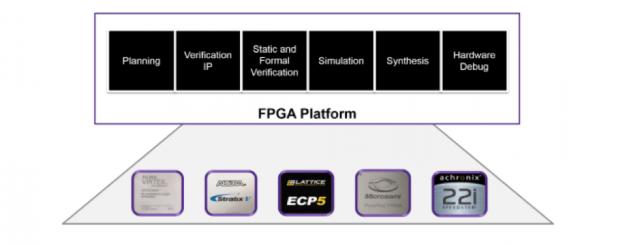

When FPGA Design Looks More Like ASIC Design

I am sure there are many FPGA designers who are quite content to rely on hardware vendor tools to define, check, implement and burn their FPGAs, and who prefer to test in-system to validate functionality. But that approach is unlikely to work when you’re building on the big SoC platforms – Zynq, Arria and even the big non-SoC devices.… Read More

Innovation in a Commodity Market

Logic simulation is a victim of its own success. It has been around for at least 40 years, has evolved through multiple language standards and has seen significant advances in performance and major innovations in testbench standards. All that standardization and performance improvement has been great for customers but can present… Read More