You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Cadence at 20nmby Paul McLellan on 08-21-2012 at 8:10 pmCategories: Cadence, EDA

Cadence has a new white paper out about the changes in IC design that are coming at 20nm. One thing is very clear: 20nm is not simply “more of the same”. All design, from basic standard cells up to huge SoCs has several new challenges to go along with all the old ones that we had at 45nm and 28nm.

I should emphasize that the paper… Read More

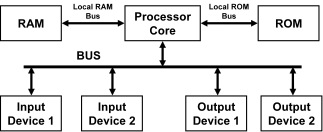

In the early 1980s the ideas and infrastructure for what would eventually be called ASIC started to come together. Semiconductor technology had reached the point that a useful number of transistors could be put onto a chip. But unlike earlier, when a chip only held a few transistors and thus could be used to create basic generic building… Read More

A Brief History of SoCsby Daniel Nenni on 08-19-2012 at 10:00 amCategories: EDA

Interesting to note; our cell phones today have more computing power than NASA had for the first landing on the moon. The insides of these mobile devices that we can’t live without are not like personal computers or even laptops with a traditional CPU (central processing unit) and a dozen other support chips. The brain, heart, and… Read More

It is obviously a truism that somewhere in an SoC there is something limiting a further increase in performance. One area where this is especially noticeable is when a Tensilica core is used to create a highly optimized processor for some purpose. The core performance may be boosted by a factor of 10 or even as much as 100. Once the core… Read More

Big processors get all the love, it seems. It’s natural, since they are highly complex beasts and need a lot of care and feeding in the EDA and fab cycle. But the law of large numbers is starting to shift energy in the direction of optimizing microcontrollers.

I mulled the math in my head for a while. In a world with 7 billion people and … Read More

Now that the mobile market is keeping us all employed, take a close look at what is actually inside those devices we can’t live without. Before SoCs you could just read the codes on the chips. Now it is all Semiconductor IP so you have to do a little more diligence to find out what is really powering your phones and tablets. One thing you… Read More

One of the really big changes about chip design is the way over the last decade or so it is no longer possible to design an SoC, a package for it to go in and the board for the package using different sets of tools and methodologies and then finally bond out the chip and solder it onto the board. The three systems, Chip-Package-System have… Read More

The Q2 numbers for smartphones are now all in and the basic story is that Google is now registering an incredible million Android phones per day, half of them made by Samsung. That’s 85% of all the smartphones shipped last quarter. Android has (per IDC) 68% market share of all smartphones out there.

Apple grew by double digit… Read More

At Semicon a few weeks ago the big news was that Intel was making a big investment in ASML as a way of funding two development programs: extreme ultra-violet (EUV) and 450mm wafers. This week TSMC announced that they would join the program too, committing 275M Euros over a five year period. They are also taking a 5% stake in ASML. ASML… Read More

As a fitting postscript to my “Brief History of the Fabless Semiconductor Industry”, semiconductor research company IC Insights compiled a list of the top semiconductor companies for the first half of 2012. As the traditional IDMs go fabless and sink in the ratings, the foundries post record gains led by TSMC at 22%, GlobalFoundries… Read More