In the largest and fastest growing categories in electronics – mobile, IoT and automotive – analog is playing an increasingly important role. It’s important in delivering high integrity power and critical signals to the design though LDO regulators and PLLs, in managing high speed interfaces like DDR and SERDES, in interfacing… Read More

Tag: power integrity

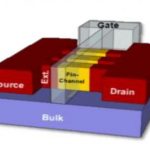

FinFETs, Power Integrity and Chip/Package Co-design

FinFETs have brought a lot of good things to design – higher performance, higher density and lower leakage power – promising to extend Moore’s law for a least a while longer. But inevitably with new advances come new challenges, especially around optimizing for power integrity in these designs.

One of these challenges is… Read More

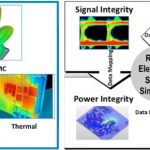

Thermal Reliability and Power Integrity for IC Design

When I designed DRAM chips at Intel back in the 1970’s we didn’t really know what the die temperature would be before taping out silicon, instead we waited for packaged parts to come back and then did our thermal measurements. IC designers today don’t have that luxury of taping out their new SoC without having … Read More

ANSYS Enters the League of 10nm Designs with TSMC

The way we are seeing technology progression these days is unprecedented. It’s just about six months ago, I had written about the intense collaboration between ANSYSand TSMCon the 16nm FinFET based design flow and TSMC certifying ANSYS tools for TSMC 16nm FF+ technology and also conferring ANSYS with “Partner of the Year” award.… Read More

ANSYS Tools Shine at FinFET Nodes!

In the modern semiconductor ecosystem we are seeing rapid advancement in technology breaking past once perceived limits; 28nm, 20nm, 16-14nm, 10nm and we are foreseeing 7nm now. Double and multi-patterning are already being seen along with complex FinFET structures in transistors to gain the ultimate advantages in PPA from… Read More

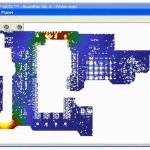

A Collaborative Approach Yields Better PI for PCBs

The power integrity (PI) of a system is an extremely important aspect to be looked at all levels – chip, package and PCB for overall reliability of the system. At the PCB level, a DC analysis, usually based on IR drop, must ensure that adequate DC voltage, satisfying all constraints of current density and temperature, is delivered… Read More

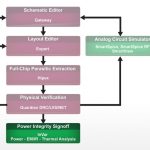

LSI’s Way of Faster & Reliable Electronic System Design

LSI Corporationstarted in 1980s and I had several encounters with it during my jobs in 1990s; not to forget the LSI chips I used to see in desktops and other electronic systems, and I’m happy to see LSI continuing today with more vigour having leadership position in storage and networking space. It provides highly reliable, high … Read More

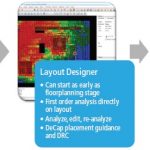

Dual Advantage of Intelligent Power Integrity Analysis

Often it is considered safer to be pessimistic in estimating IR-drop to maintain power integrity of semiconductor designs; however that leads to the use of extra buffering and routing resources which may not be necessary. In modern high speed, high density SoCs having multiple blocks, memories, analog IPs with different functionalities… Read More

Mission Critical Role of Unmanned Systems – How to fulfill?

Do we ever imagine what kind of severe challenges mission critical unmanned systems in air, land and underwater face? They are limited in space and size; have to be light in weight, flexible in different types of operations and at the same time rugged enough to work in extreme climatic conditions. That’s not enough; amidst these … Read More

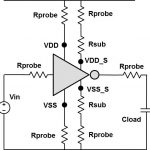

Power integrity: ground, and other fairy tales

Ground. It’s that little downward-pointing triangle that somehow works miracles on every schematic. It looks very simple until one has to tackle modern power distribution network (PDN) design on a board with high speed and high power draw components, and you soon discover ground is a complicated fairy tale with a lot of influences.… Read More