You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

By Todd Burkholder and Per Viklund, Siemens EDA

The landscape of advanced IC packaging is rapidly evolving, driven by the imperative to support innovation on increasingly complex and high-capacity products. The broad industry trend toward heterogeneous integration of diverse die and chiplets into advanced semiconductor… Read More

2.5D and 3D multi-die design is rapidly moving into the mainstream for many applications. HPC, GPU, mobile, and AI/ML are application areas that have seen real benefits. The concept of “mix/match” for chips and chiplets to form a complex system sounds deceptively simple. In fact, the implementation and analysis techniques required… Read More

Artificial intelligence (AI) is driving a transformation in data center infrastructure, necessitating cutting-edge technologies to meet the growing demands of AI workloads. As AI systems scale up and out, next-gen compute servers, switches, optical-electrical links, and flexible, redundant networking solutions are … Read More

A vital benefit of advanced EM simulations is their ability to take on complicated physical test setups, substituting far easier virtual tests yielding accurate results earlier during design activities. The latest release of Keysight PathWave ADS 2023 continues speeding up engineering workflows. Let’s look at three… Read More

We all know signal integrity and power integrity are becoming more important for advanced design. Like package engineering, the obscure and highly technical art of SI/PI optimization has taken center stage in the design process. And the folks who command expertise in these areas have become the rock stars of the design team. I … Read More

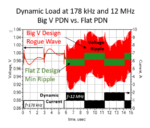

Advanced board designs are fertile ground for misbehavior in time and frequency domains. Relying on intuition, then waiting until near-final product for power integrity (PI) or EMI testing almost guarantees board respins are coming. Lumped-parameter simulations of on-board power delivery networks (PDNs) struggle with … Read More

The Signal Integrity Journal recently held a half day Electronic Systems SI/PI Forum that included presentations from industry leaders covering key design topics for signal integrity and power integrity engineers. The event was sponsored by Cadence. The keynote for the event was presented by Istvan Novak, principal signal… Read More

Power integrity analysis in large chip designs is especially challenging thanks to the huge dynamic range the analysis must span. At one end, EM estimation and IR drop through interconnect and advanced transistor structures require circuit-level insight—very fine-grained insight but across a huge design. At the other, activity… Read More

Semiconductor technology advances have a way of rewriting the rule book. As process geometries shrink, subtle effects graduate to mainstream problems. Performance curves can become inverted. And no matter what else occurs, low power demands are constantly reducing voltage and design margins along with it. Sometimes these… Read More

I had the opportunity to preview an upcoming SemiWiki webinar on IR drop and power integrity. These topics, all by themselves, have real stopping power. Almost everyone I speak with has a story to tell about these issues in a recent chip design project. When you combine hot topics like this with a presentation that details the collaboration… Read More