Getting your tape-out done on time is hard, but can it be made easier? That was the main topic of Mentor’s Calibre Panel held at DAC 2018, attended by a few key players in IC design ecosystem: Bob Stear, VP of Marketing at Samsung represented the foundry side; from the IP side, Prasad Subramaniam, VP of eSilicon for R&D and Technology;… Read More

Tag: finfet

Imec technology forum 2018 – the future of scaling

At the Imec technology forum in Belgium, Dan Mocuta and Juliana Radu presented “Evolution and Disruption: A Perspective on Logic Scaling and Beyond”, I also had a chance to sit down with Dan and discuss the presentation.

Device scaling

Scaling of devices will only get you so far, you need to look at new devices and new… Read More

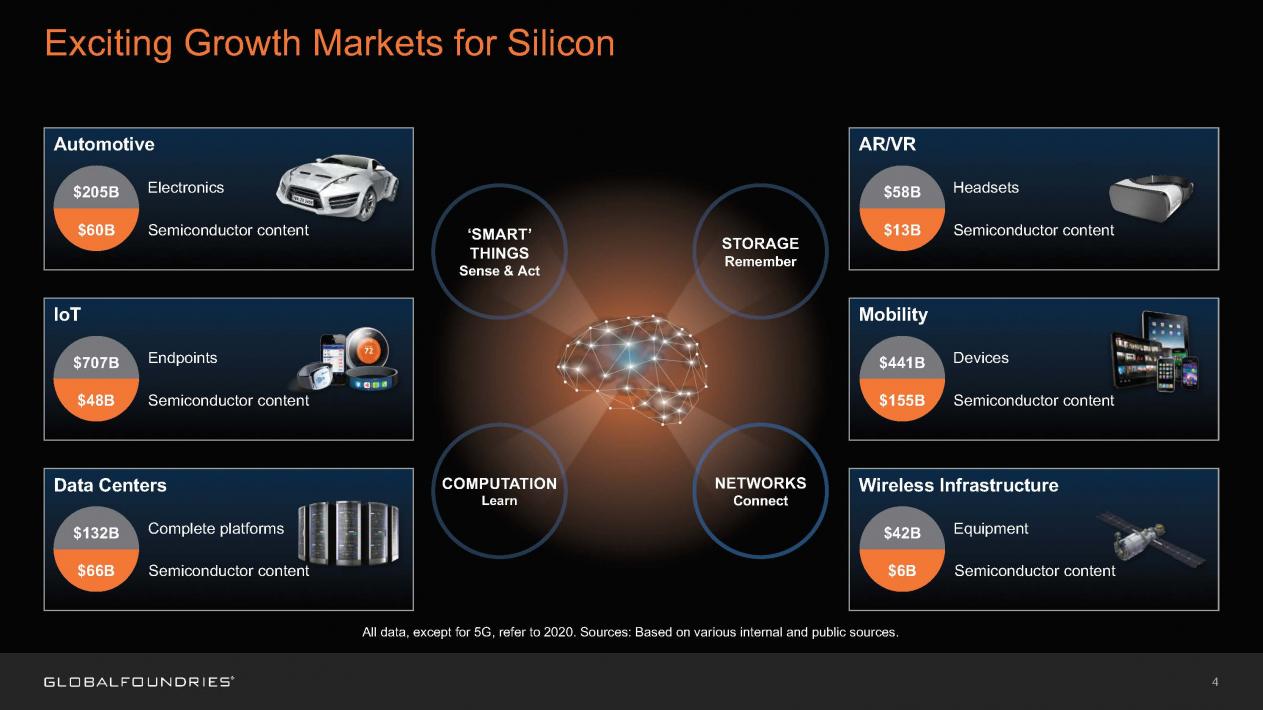

Imec Technology Forum: Gary Patton of GLOBALFOUNDRIES

The imec technology forum was held in Belgium last week. At the forum I had a chance to sit down with Gary Patton the CTO of GLOBALFOUNDRIES (GF) for an interview and he also presented “Enabling Connected Intelligence – Technology innovation: Enablers for an intelligent future” at the forum. In this article … Read More

SPICE Model Generation by Machine Learning

It was 1988 when I got into SPICE (Simulation Program with Integrated Circuit Emphasis)while I was characterizing a 1.5 μm Standard cell library developed by students at my Alma-Mata Furtwangen University in Germany. My professor Dr. Nielinger was not only my advisor he also wrote the first SPICE bible in German language. At that… Read More

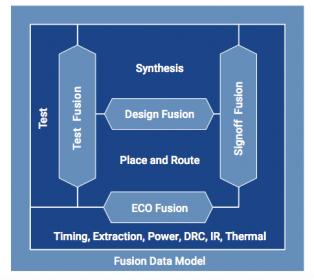

Retooling Implementation for Hot Applications

It might seem I am straying from my normal beat in talking about implementation; after all, I normally write on systems, applications and front-end design. But while I’m not an expert in implementation, I was curious to understand how the trending applications of today (automotive, AI, 5G, IoT, etc.) create new demands on implementation,… Read More

TSMC Technologies for IoT and Automotive

At TSMC 2018 Silcon Valley Technology Symposium, Dr Kevin Zhang, TSMC VP of Business Development covered technology updates for IoT platform. The three growth drivers in this segment namely TSMC low power, RF enhancement and embedded memory technology (MRAM/RRAM) reinforced both progress and growth in global semiconductor… Read More

TSMC Technologies for Mobile and HPC

During TSMC 2018 Technology Symposium, Dr. B.J. Woo, TSMC VP of Business Development presented market trends in the area of mobile applications and HPC computing as well as shared TSMC progress in making breakthrough efforts in the technology offerings to serve these two market segments.

Both 5G and AI are taking the center stage… Read More

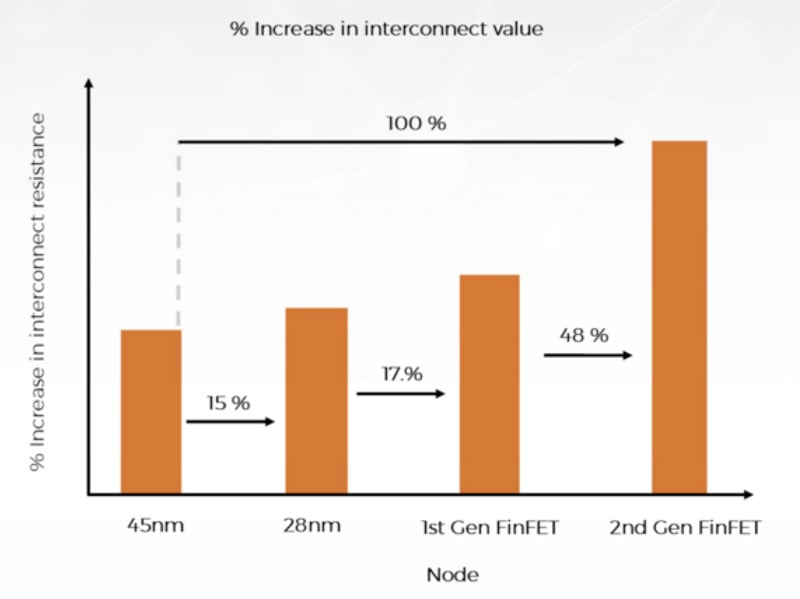

imec and Cadence on 3nm

One of the more frequent questions I get, “What is next after FinFETs?” is finally getting answered. Thankfully I am surrounded by experts in the process technology field including Scotten Jones of IC Knowledge. I am also surrounded by design enablement experts so I really am the man in the middle which brings us to a discussion between… Read More

Monitoring Process, Voltage and Temperature in SoCs, webinar recap

Have you ever wondered how process variation, thermal self-heating and Vdd levels affect the timing and yield of your SoC design? If you’re clock specification calls for 3GHz, while your silicon is only yielding at 2.4GHz, then you have a big problem on your hands. Such are the concerns of many modern day chip designers. To… Read More

What does a Deep Learning Chip Look Like

There’s been a lot of discussion of late about deep learning technology and its impact on many markets and products. A lot of the technology under discussion is basically hardware implementations of neural networks, a concept that’s been around for a while.

What’s new is the compute power that advanced semiconductor technology… Read More