I think by now there has been good level of discussion on FinFET technology at sub-20 nm process nodes and this is an answer to ultra dense, high performance, low power, and billion+ gate SoC designs within the same area. However, it comes with some of the key challenges with respect to power, noise and reliability of the design. A FinFET… Read More

Tag: finfet

Key Collaboration to Enable Designs at Advanced Nodes

In the semiconductor ecosystem, several partners (or better to say stakeholders) join together in the overall value chain to finally output the most coveted chip, err I should say SoC these days. It becomes really interesting when we start analyzing the real value added by each of them, none appears to be less. Well, then to whom … Read More

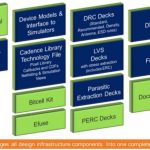

ANSYS Tools Shine at FinFET Nodes!

In the modern semiconductor ecosystem we are seeing rapid advancement in technology breaking past once perceived limits; 28nm, 20nm, 16-14nm, 10nm and we are foreseeing 7nm now. Double and multi-patterning are already being seen along with complex FinFET structures in transistors to gain the ultimate advantages in PPA from… Read More

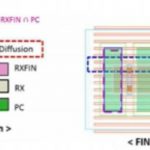

Place & Route with FinFETs and Double Patterning

Place & route in the 16/14nm era requires a new approach since it is significantly more complex. Of course, every process generation is more complex than the one before and the designs are bigger. But modern processes have new problems. The two biggest changes are FinFETs and double patterning.

FinFETs, as I assume you know,… Read More

TSMC Delivers First FinFET ARM Based SoC!

Right on cue, TSMC announces 16nm FinFET production silicon. I believe this is the original version of FinFET versus 16FF+ which is due out in 1H 2015. I will confirm this next week at the TSMC OIP event in San Jose, absolutely. Either way this is excellent news for the fabless semiconductor ecosystem and I look forward to the first … Read More

Samsung 14nm FinFET Design with Cadence Tools

The first consumer products with 20nm processing are arriving in 2014 like the 2 billion transistor A8 chip in the iPhone 6, however at the 14nm node there are new designs underway to continue the trend of Moore’s Law. To get a better feel for the challenges of designing with 14nm FinFET technology I watched a 23 minute video … Read More

Sidense overlays OTP on TSMC 16nm FinFET

Process shrinks, which have served us well for most of the Moore’s Law journey, are reaching their limits. For switching transistors, the biggest problems of leakage current and gate oxide vulnerability in planar MOSFETs have led the industry to new 3D microstructures such as FinFET. For non-volatile memory, the problem is generally… Read More

Design & EDA Collaboration Advances Mixed-Signal Verification through VCS AMS

Last week it was a rare opportunity for me to attend a webinar where an SoC design house, a leading IP provider and a leading EDA tool provider joined together to present on how the tool capabilities are being used for advanced mixed-signal simulation of large designs, faster with accuracy. It’s always been a struggle to combine design… Read More

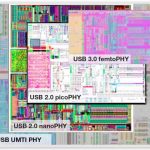

USB 3.0 IP on FinFET may stop port pinching

Sometimes a standard is a victim of its own success, at least for a while as the economics catch up to the technology. When a standard like USB 3.0 is announced, with a substantial performance increase over USB 2.0, some of the use cases come on board right away. Others, where vendors enjoy a decent ROI with good-enough performance,… Read More

Intel 14nm is NOT in Production Yet!

Okay, maybe I’m the only one questioning Intel 14nm yield but I think it will be an interesting discussion in the comments section. Here are the questions I would have asked Intel during their recent 14nm PR tour: Has the P1272 process been rolled out to the production fabs in OR, AZ, and Ireland? Is the process officially in production… Read More