You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

For several decades now consumers like me have enjoyed using mobile devices including:

- Transistor radios, my first one had just 6 discreet transistors in the 1960’s

- HP 21 Calculator, used in college with Reverse Polish Notation, circa 1976

- Zenith Data Systems laptop, with two floppy drives, 1980’s

- Palm Pilot V,

…

Read More

I first heard about Andrew Yang back in 1993 when he founded a Fast SPICE company called Anagram, then acquired by Avant! in 1996. Andrew’s latest EDA company Apache Design, Inc.was started in 2001, then acquired by ANSYS in 2011. Most EDA mergers simply don’t work because of one or more reasons, like:

…

Read More

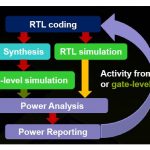

It’s a classic and creative example of design and EDA tool community getting together, exploiting tool capabilities and developing flows which add value to all stake holders including the end consumer. We know power has become extremely important for battery life in smart phones, high performance servers, workstations, notebooks… Read More

What do nVidia, Freescale and GlobalFoundries have in common? They are semiconductor companies? They are ARM licensees? They are doing 28nm chips? They all have the letter ‘a’ in their names?

All true, but that’s not what I was thinking of. But the letter ‘a’ is a clue since Apache (and Ansys) begin with ‘a’. All three companies have… Read More

Nvidia designs some of the most powerful graphics chips and systems in the world, so I’m always eager to learn more about their IC design methodology. This week I’ve had the chance to talk with Ting Ku, Director of Engineering at Nvidia about his DAC talkin the Apache booth in exactly two weeks from today. Registration… Read More

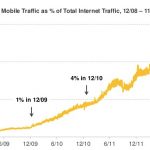

Mobile devices are taking over the world. If you want lots of graphs and data then look at Mary Meeker’s presentation that I blogged about earlier this week. The graph on the right is just one datapoint, showing that mobile access to the internet is probably up to about 15% now from a standing start 5 years ago.

Of course, one obvious… Read More

Watch the Clockby Paul McLellan on 03-05-2013 at 2:24 pmCategories: Ansys, Inc., EDA

Clock gating is one of the most basic weapons in the armoury for reducing dynamic power on a design. All modern synthesis tools can insert clock gating cells to shut down clocking to registers when the contents of the register are not changing. The archetypal case is a register which sometimes loads a new value (when an enable signal… Read More

After a show like DesignConwraps up we get a chance to ask ourself what it all meant, and how was this year different than last year. Reading through many posts about DesignCon I came to discover that the Awards at DesignCon are less contentious than at CES, and also that ANSYSreceived a DesignVision awardfor the 2nd year running. … Read More

DesignConis next week in Santa Clara, so today I spoke with Mark Ravenstahlfrom ANSYS to get an idea of what to expect at the conference and trade show.

… Read More

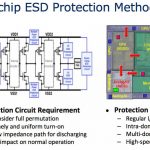

In Pune at the start of the month, Norman Chang, Ting-Sheng Ku, Jai Pollayil of Apache/Ansys and NVIDIA presented and ESD check methodologywith Fast Full-chip Static and Macro-level Dynamic Solutions . ESD stands for Elecro-Static Discharge and is basically injecting very high static voltages (think how your hand gets charged… Read More