Since a few years, I have been following up Ansys Apachetools for semiconductor design, verification and sign-off. RedHawk is the most prominent platform of tools from Ansys, specifically for Power, Noise and Reliability Sign-off. It has witnessed many open endorsements from several of Ansyscustomers through open presentations,… Read More

Tag: ansys

Apache Design @ #51DAC Must See!

Register to hear industry experts from top semiconductor companies share their best practices that enable the next generation of high-performance, low power designs for mobile, automotive and other applications. Meet our technologists for in-depth presentations, case studies and demos on the industry’s leading simulation… Read More

IC Power Noise Reliability for FinFET Designs

Reliability for ICs is a big deal because the last thing that you want to do is ship a new part only to find out later in the field that there are failures not being caught by testing. I’ve already had two consumer products fail this year because of probable reliability issues: My MacBook Pro with 16GB of RAM started rebooting caused… Read More

LSI’s Way of Faster & Reliable Electronic System Design

LSI Corporationstarted in 1980s and I had several encounters with it during my jobs in 1990s; not to forget the LSI chips I used to see in desktops and other electronic systems, and I’m happy to see LSI continuing today with more vigour having leadership position in storage and networking space. It provides highly reliable, high … Read More

IC/Package/Board – Power, Noise and Reliability from ANSYS (Apache DA) at DAC

ANSYS acquired Apache Design Automation back in June 2011and three years later the name “Apache” is being subdued in favor of using just ANSYS. One thing that I noticed right away was a DACfocus on having actual ANSYS customers talk about their hands-on experience using the EDA tools. The following seven customers… Read More

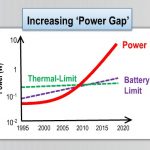

Early RTL Power Analysis and Reduction

Power analysis and reduction for SoC designs is a popular topic because of our consumer electronics dominated economy, and the need to operate devices on a battery source for the maximum time before a recharge. Just from my desk I can see multiple battery-powered devices: Laptop, tablet, smart phone, e-book reader, bluetooth … Read More

Who Won the DesignVision Awards at DesignCon this year?

The Seattle Seahawks had an awesome victory in the SuperBowl against the Denver Broncos, so folks living here in the Pacific Northwest are feeling proud and optimistic. The recent DesignConconference and exhibit ended 10 days ago and there were also victors announced in terms of the annual DesignVision awards that have three … Read More

Mission Critical Role of Unmanned Systems – How to fulfill?

Do we ever imagine what kind of severe challenges mission critical unmanned systems in air, land and underwater face? They are limited in space and size; have to be light in weight, flexible in different types of operations and at the same time rugged enough to work in extreme climatic conditions. That’s not enough; amidst these … Read More

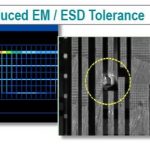

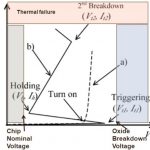

Full Chip ESD Sign-off – Necessary

As Moore’s law keeps going, semiconductor design density on a chip keeps increasing. The real concern today is that the shrinkage in technology node has rendered the small wire geometry and gate oxide thickness (although fine in all other perspectives) extremely vulnerable to ESD (Electrostatic Discharge) effects. More than… Read More

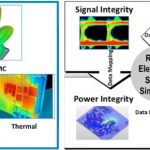

Low-Power Design Webinar – What I Learned

You can only design and optimize for low-power SoC designs if you can actually simulate the entire Chip, Package and System together. The engineers at ANSYS-Apachehave figured out how to do that and talked about their design for power methodology in a webinar today. I listened to Arvind Shanmugavel present a few dozen slides and… Read More