This year is most notably the 50th anniversary of Moore’s Law. It is also the 25th anniversary of Concept Engineering. They were founded in 1990 in Freiburg Germany. They started by providing automatic schematic generation from netlist. They sold primarily to other EDA companies and to internal development groups in semiconductor… Read More

Tag: aldec

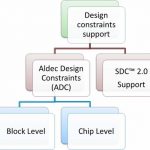

Aldec packs 6 UltraScale parts on HES-7

A few months ago, when the Xilinx UltraScale VU440 FPGA began shipping, one of the immediate claims was a quad-FPGA-based prototyping board touted as “Godzilla’s Butcher on Steroids”. That was a refreshing and creative PR approach, frankly. I’m always careful with less creative terms like “world’s biggest” or “world’s fastest”,… Read More

How many coats cover this SoC?

“Most interior paint covers with one coat.” Back when there was something called a newspaper, this was an actual blurb in the home improvement pages, section 3, part 8, page 5 of the Chicago Tribune on Sunday, August 13, 1961. Even then, marketers were catering to consumers looking to cut corners and save time, and one-coat coverage… Read More

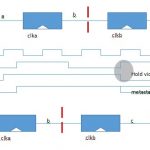

Writing the unwritten rules with ALINT-PRO-CDC

EDA verification tools generally do a great job of analyzing the written rules in digital design. Clock domain crossings (CDCs) are more like those unwritten rules in baseball; whether or not you have a problem remains indefinite until later, when retaliation can come swiftly out of nowhere.

Rarely as overt or dramatic as a bench-clearing… Read More

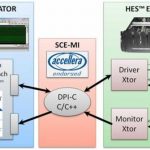

Aldec increasing the return on simulation

Debate rages about which approach is better for SoC design: simulation, or emulation. Simulation proponents point to software saving the need for expensive hardware platforms. Emulation supporters stake their claims on accuracy and the incorporation of real-time I/O. A few years back, some creative types coined the term SEmulation,… Read More

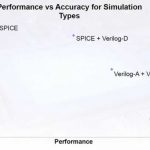

Verilog-AMS connects T-SPICE and Riviera-PRO

With advances in available IP, mixed signal design has become much easier. Mixed signal verification on the other hand is becoming more complicated. More complexity means more simulation, and in the analog domain, SPICE-based techniques grinding away on transistor models take a lot of precious time. Event-driven methods like… Read More

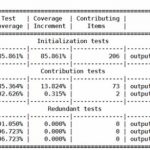

Verification plans overcome hope-based coverage

Coverage is an important yet elusive metric for design verification. It often seems 90% of coverage comes with 10% of the effort, and getting the final 10% covered takes the remaining 90% of a project. Usually, it takes another tool or methodology to get at the 10% the first tool missed. With 100% closure difficult, most teams inspect… Read More

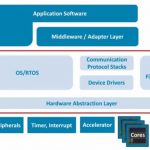

3 reasons to focus on hardware dependent software

Why is software for modern SoCs so blasted expensive to develop? One reason is more software is being developed at the kernel layer – hardware dependent software, or HdS. Application software often assumes the underlying hardware, operating system, communication stacks, and device drivers are stable. For HdS, this flawed assumption… Read More

Dominating FPGA clock domains and CDCs

Multiple clock domains in FPGAs have simplified some aspects of designs, allowing effective partitioning of logic. As FPGA architectures get more flexible in how clock domains, regions, or networks are available, the probability of signals crossing clock domains has gone way up.… Read More

September is Semiconductor Design Webinar Month!

The nice thing about webinars is that if you register for the live one and you can’t attend you will still get first notice when the replay goes up. The other nice thing is that you can read a blog review of a webinar or whitepaper on SemiWiki first to see if it is worth your time. If you do attend a webinar you can also post a review of… Read More