You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

In the third installment of this series we discussed the status of DRAM scaling and Moore’s law. In this installment we will tackle logic. The focus will be on foundry logic.

Logic technology challenges

In the second installment of this series we discussed constant electric field scaling. As we mentioned in that installment at … Read More

A tremendous number of chips being designed for today’s products require some sort of onboard data storage. The size of these needs range from a handful of bytes, for trim and calibration storage, to something much more substantial like boot code storage. In both of these examples the storage ideally should be nonvolatile, with… Read More

At the end of last month during ISSCC there was a forum organized by the SOI Consortium. It took place in San Francisco at the Palace Hotel (which, if you have never been there, is famous for converting its old entryway for carriages into an amazing dining room, and for a bar with a huge painting by Maxfield Parrish of the Pied Piper valued… Read More

Doing a modern SoC design is all about assembling IP and adding a small amount of unique IC design for differentiation (plus, usually, lots of software). If you re designing in a mature process then there is not a lot of difficulty finding IP for almost anything. But if you are designing in a process that has not yet reached high-volume… Read More

Various foundries have made announcements about licensing FD-SOI technology from ST Microelectronics and then fallen quiet. GlobalFoundries made an announcement a couple of years ago. Samsung made an announcement just before DAC last year. But neither company has said anything much since. Of course the big noise at 14/16nm… Read More

I would like to further discuss this graphic (presented during IP-SoC 2014 by John Koeter, VP of Marketing IP and prototyping, Synopsys) and focus on Active Design and Tapeouts at 28nm. In fact the very first activity appeared in Q1 2007, but it was only during 2010 that 28nm become popular, after the first Tapeouts coming in Q1 and… Read More

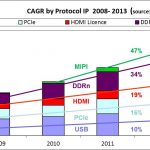

… were given to an ever shrinking audience. This is IP-SoC paradox: audience has enjoyed very good presentations made by Cadence, Synopsys or ST-Microelectronic, to name just a few. As far as I am concerned, I was happy to present the “Interface IP Winners and Losers (Protocols)” in the amphitheater during the first day, enjoying… Read More

Xilinx announced their quarterly results a couple of days ago. Technically it is their Q2 2015. Sales were $604M and profitability was significantly higher than expected at $0.62/share. But that is not the most interesting thing about these calls. There is the Xilinx vs Altera story. And then there are tealeaves to be read about… Read More

In our rush to shrink SoC nodes more and more to achieve better performance and more complex devices, we may have forgotten a passenger in the back seat: non-volatile memory. There has been little discussion of this in the pages of SemiWiki until now. Let’s give it a closer look.

Embedded flash has usually been associated with microcontrollers,… Read More

There has been a lot of controversy about whether FD-SOI is or is not cheaper to manufacture than FinFET. Since right now FinFET is a 16nm process (22nm for Intel) and FD-SOI is, for now, a 28nm process it is not entirely clear how useful a comparison this is. Scotten Jones has very detailed process cost modeling software (that is what… Read More