Talk about an unusual position. Intel finds themselves very much currently outside when it comes to mobile SoCs for phones and tablets. After several attempts at soul-searching and a true understanding of the term “low-power” (not meaning 3W, but instead < 1W), they finally have a part – in the form of “Medfield”, aka the Atom… Read More

imec on the Benefits of ASICs and How to Seize ThemIn an era where product differentiation increasingly depends…Read More

imec on the Benefits of ASICs and How to Seize ThemIn an era where product differentiation increasingly depends…Read More MZ Technologies Launches Advanced Packaging Design Video SeriesIn a significant move aimed at empowering semiconductor…Read More

MZ Technologies Launches Advanced Packaging Design Video SeriesIn a significant move aimed at empowering semiconductor…Read More Superhuman AI for Design Verification, Delivered at ScaleThere is a new breed of EDA emerging.…Read More

Superhuman AI for Design Verification, Delivered at ScaleThere is a new breed of EDA emerging.…Read More The Quantum Threat: Why Industrial Control Systems Must Be Ready and How PQShield Is Leading the DefenseIndustrial control systems (ICS) underpin the world’s most…Read More

The Quantum Threat: Why Industrial Control Systems Must Be Ready and How PQShield Is Leading the DefenseIndustrial control systems (ICS) underpin the world’s most…Read MoreCEVA is the undisputed DSP worldwide leader

Anybody working in the wireless handset segment probably knows that CEVA is the provider of DSP IP cores, and if you are simply a wireless handset user, you should know that the baseband digital signal processing is the function allowing your phone to process the RF (analog) signal coming from the outside world. If you have been involved… Read More

Analyzing Cortex Performance

CPAK sounds like something politicians create to collect money, but in fact it is a Carbon Performance Analysis Kit. It consists of models, reference platform, initialization software (for bare metal CPAKs) or OS binary (for Linux and Android based CPAKs). They are (or will soon be) available for ARM Cortex A9, ARM Cortex A15 and… Read More

Piper Jaffray Chip Analyst Spanks Intel!

This just in from Tech Trader Daily, quoting Piper Jaffraychip analyst Gus Richard:

The whole issue for Qualcomm, based on Richard’s conversations with industry types, is that the company has started making its “MSM8960″ chip with Taiwan Semiconductor Manufacturing (TSM) only two to three quarters after TSM introduced… Read More

MIPS, ARM, ARC, Imagination, Ceva

The Linley Group, whose conference on mobile I recently attended, has some interesting data about the processor core market. Firstly, the numbers are big: CPU cores shipped in over 10 billion chips last year which is up 25% on last. ARM has a share of 78% of that entire market. The big surprise to me was the #2 was not MIPS but Synopsys… Read More

View from the top: Michael Buehler-Garcia

Yesterday I met with Michael Buehler-Garcia, Director of Marketing at Mentor Graphics for Calibre in Wilsonville, Oregon to get an update on what’s coming up at DAC, the premier conference and trade show for our industry.

Cadence Update 2012!

What’s new at Cadence? Quite a bit actually. I have always been a Cadence fan, I mean really, they gave birth to modern EDA. Unfortunately, Cadence really lost me during the Avant! legal action, the Mike Fister years, and EDA360. Recently, however, Cadence has made some big changes that will definitely get them back on my good side.… Read More

TSMC Tops Intel, Samsung in Capacity!

While I was marlin fishing in Hawaii last week I missed some interesting comments from TSMC executives at the Technology Symposium in Taiwan, a much different show than the one here in San Jose I’m told. It is good to see TSMC setting the record straight and taking a little credit for what they have accomplished! I’m sorry I missed it… Read More

DAC: Finding Somewhere to Eat

I am not going to attempt to give you any restaurant advice beyond what I’ve already done by listing the good places near the conference center. San Francisco reputedly has over 3000 restaurants so I don’t know anything about more than a tiny fraction. However, with that many restaurants, most places are pretty good. If not, they … Read More

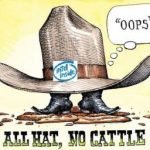

Intel Foundry All Hat No Cattle?

If you look real close at the #49 DAC floor plan you will see the tiny Intel booth dwarfed by those of TSMC, GlobalFoundries, Samsung, and ARM. The number one semiconductor company in the world does not have the budget for the cornerstone conference of the semiconductor ecosystem? Oh my…… Intel has a big foundry hat and no cattle… Read More

Quantum Computing Technologies and Challenges