A very astute gentleman said to me a few years ago that he’d seen a lot of networking technology come and go – Token Ring, FDDI, Fibre Channel, InfiniBand – but the only one that held up over time was Ethernet.… Read More

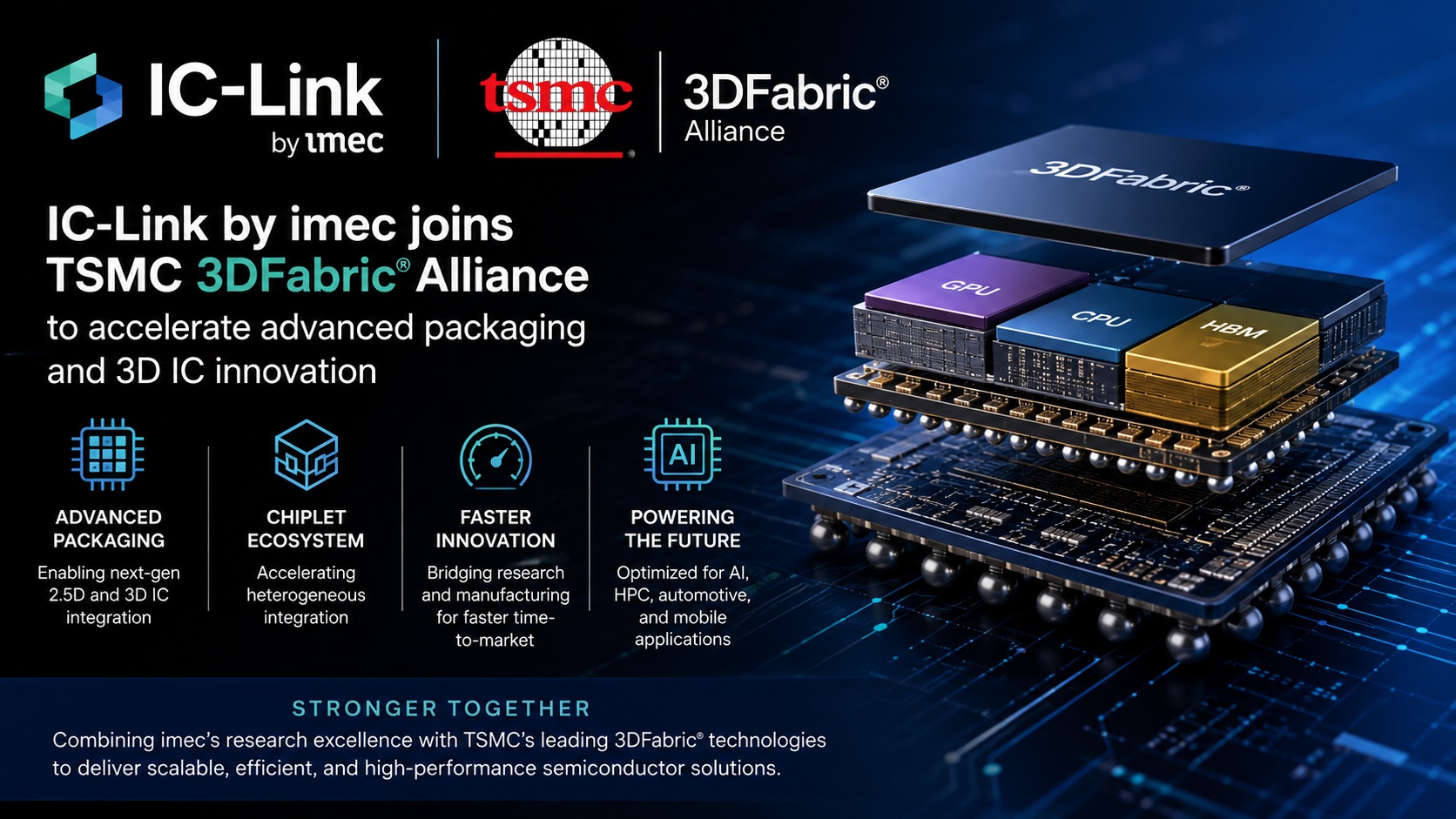

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scalingimec announced that IC-Link by imec has joined…Read More

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scalingimec announced that IC-Link by imec has joined…Read More From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read MoreAnyone Can Build a Phone

Today’s Dilbert cartoon is about how anybody can build a smart phone. As if it was a technical problem these days. But back in the mid-90s it really was. All the contract manufacturers like Solectron and others figured that since they could build a PC they could build a phone. It turned out that building radios was really hard.… Read More

Will Andy Grove Save Intel By Recruiting Jen Hsun Huang?

Intel may not know it but they are entering a crises moment due to the announced resignation of Paul Otellini that will not take place until May 2013. A six-month funeral with a 100,000 mourning employees will not calm customers who question whether to stick with the x86 PC roadmap much less the Atom mobile processors. A more dramatic… Read More

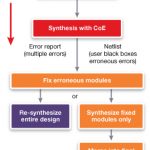

Second FPGA to the right, and straight on ‘til it works

In a fantasy world where there were no coding errors or integration issues, FPGA designs would fly straight through synthesis easily and quickly. Maybe that world does exist somewhere. For the rest of us, who have experienced the agony of running a large FPGA design – again – only to find another error and have to start over, there … Read More

Interview with David Eggleston on Rambus-Unity CMOx

by Christie Marrian of ReRAM-Forum.com

Unity Semiconductor is a true veteran in the emerging memory/ReRAM field and was recently acquired by Rambus “one of the world’s premier technology licensing companies”. I must admit to being somewhat surprised by this acquisition when I first heard about it. Was this another example… Read More

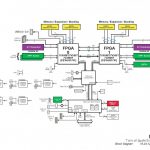

ASIC Prototyping: Dini Group and Tektronix

Collaboration in EDA is nothing new, however you may not be aware of how the Dini Group and Tektronix have worked together on an FPGA prototyping platform to address issues like debugging with full visibility across an entire multi-FPGA design. At SemiWiki we’ve blogged a couple of times so far about the new debug approach… Read More

Dear Santa, please bring technology that brings us together

Dear Santa,

It has been many years since I have written you. I was taught never to ask anyone for anything for myself, that it is a presumptuous and selfish thing to do, so this is not for me. I know you are busy filling the wish lists of children everywhere, but wanted to take a moment to ask for your help for everyone.… Read More

CEVA also bid to acquire MIPS… ARM still staying quiet?

We have seen in a previous post that Imagination Technologies has proposed to buy MIPS, in fact “MIPS operating business and certain patent properties, as well as license rights to all of the remaining patent properties”. Translated into understandable language Imagination has offered $60M for MIPS Processor IP core portfolio,… Read More

Tanner EDA Tops 1,200 Active Customers!

It is always nice to see when an EDA company grows organically, versus inorganically by acquiring friends and foes. It is also nice to see when an EDA company invests in the fabless semiconductor ecosystem because, as we know, we are all in this together.

Tanner EDA celebrated its 25th anniversary this year by adding 149 new customers… Read More

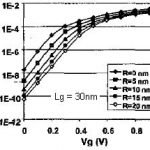

Introduction to FinFET Technology Part III

The preceding two Semiwiki articles in this thread provided an overview to the FinFET structure and fabrication. The next three articles will discuss some of the unique modeling requirements and design constraints that FinFET’s introduce, compared to planar FET technology.

Due to the complexity of FinFET modeling – … Read More

Crossing the Yield Cliff: IDP V6 and the Future of Manufacturing Forecasting